Пожалуйста, обратите внимание, что пользователь заблокирован

В этой теме хочу разместить цикл статей по началу работы с семейством ПЛИС (FPGA) фирмы Xilinx.

Начиная с установки среды разработки и заканчивая созданием простенького генератора хешей для взлома криптоалгоритма A5/1 используемого в GSM. Коснемся вопроса распараллеливания вычислений, отладки, работы с программаторами и методами загрузки прошивок.

К сожалению, некоторые материалы буду писать не в строгой идеологической последовательности, т.к. не всегда есть возможность "выдернуть" какую-то железку или вирт.машину из основных проектов, но в первом сообщении (этом) позже появится список ссылок и оглавление, где материал можно будет повторить-почитать уже более последовательно.

Так же, здесь будет больше практики, нежели чем теории. Основной упор - именно на "хакерское" применение ПЛИС, т.е. для использования их в качестве сопроцессоров для ускорения взломов паролей и т.д.

Часть 1. Установка среды разработки (IDE). Рабочее место ПЛИСовода.

Для начала - давайте разберем один момент.

У Xilinx'а, все ПЛИСы имеют 2 идентификатора - это название и серия.

У Xilinx'а, все ПЛИСы имеют 2 идентификатора - это название и серия.

Основные названия - Spartan, Artix, Virtex, Kintex

Серии - 3, 4, 5, 6, 7 и так далее. Отдельно еще есть линейка UltraScale.

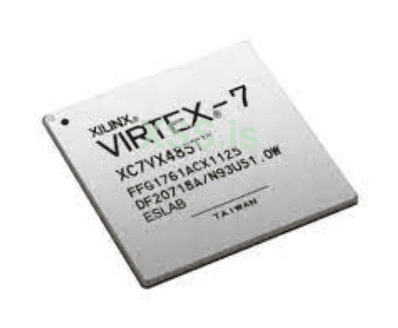

Каждой комбинации, например - Spartan 3, соответствует определенный "размер" чипа, количество логических ячеек. Например, Spartan3-100, содержит в себе 100 000 логических элементов. Virtex4-75 - 75000 лог ячеек, но при этом он сам по себе быстрее чем Spartan и логические элементы (LUT'ы) у него устроены более сложно, что позволяет запускать более сложный софт, но занимать при этом меньше емкости чипа. Так же чипы бывают в корпусах с разным количеством ножек, с наличием или отсутствием PowerPC ядер и так далее.

Прошу заметить, что тут я сильно упрощаю - так как обещал минимум теории.

На первое время, нужно уяснить - что вся линейка чипов делится на "до СЕДЬМОЙ" серии, и "ПОСЛЕ седьмой" серии.

На первое время, нужно уяснить - что вся линейка чипов делится на "до СЕДЬМОЙ" серии, и "ПОСЛЕ седьмой" серии.

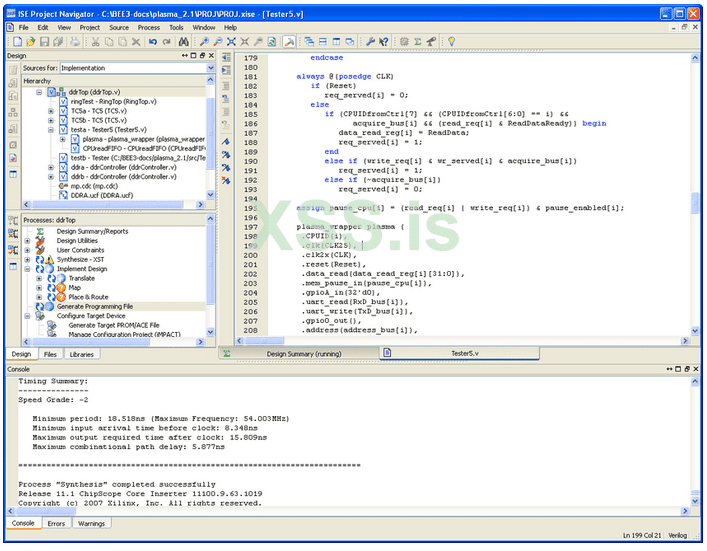

Это принципиально важный момент, так как микропрограммы чипов например Virtex3, Kintex 5, Virtex 7 (т.е. все что до семерки, включая ее) - разрабатываются в устаревшем IDE Xilinx ISE:

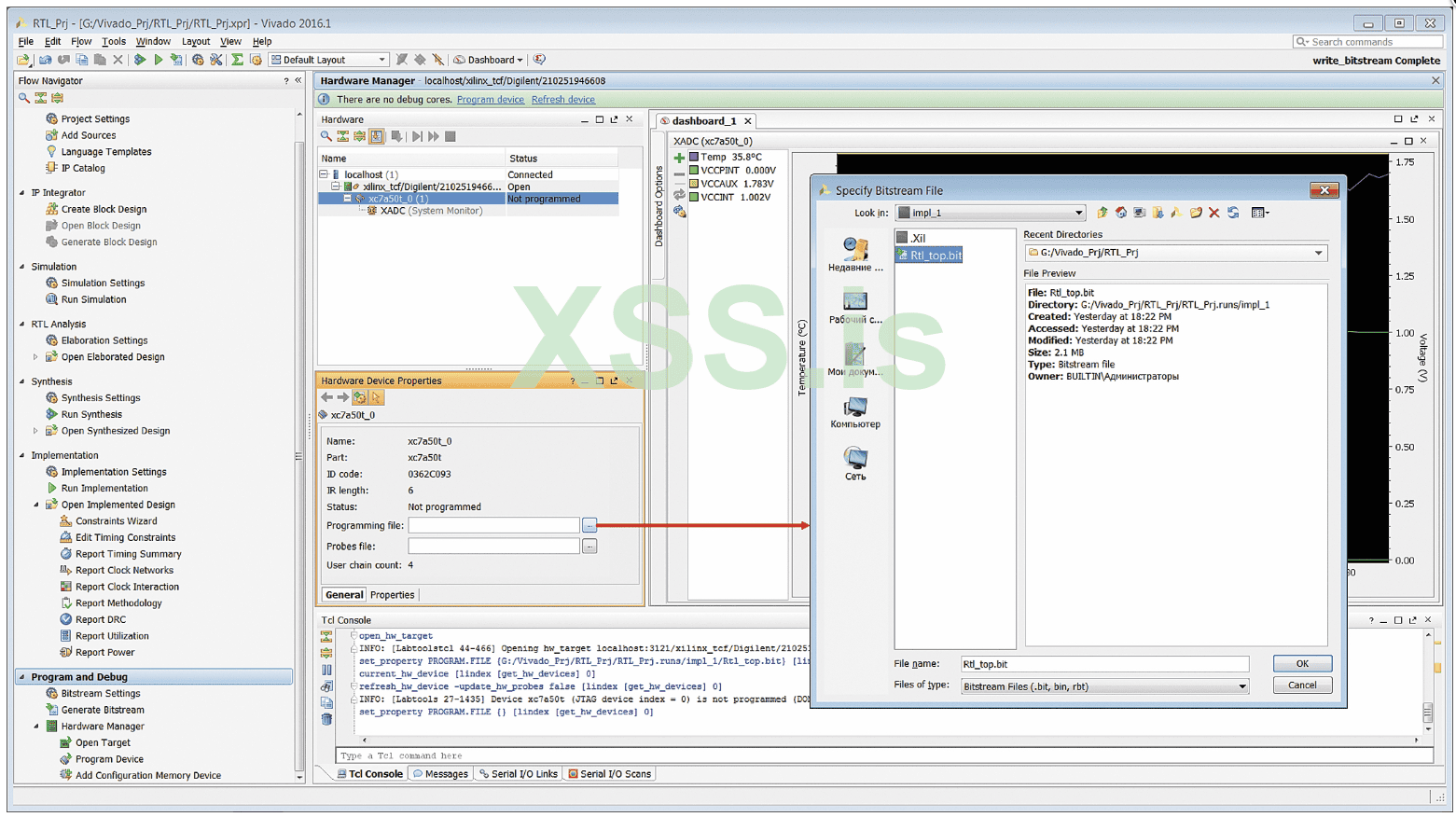

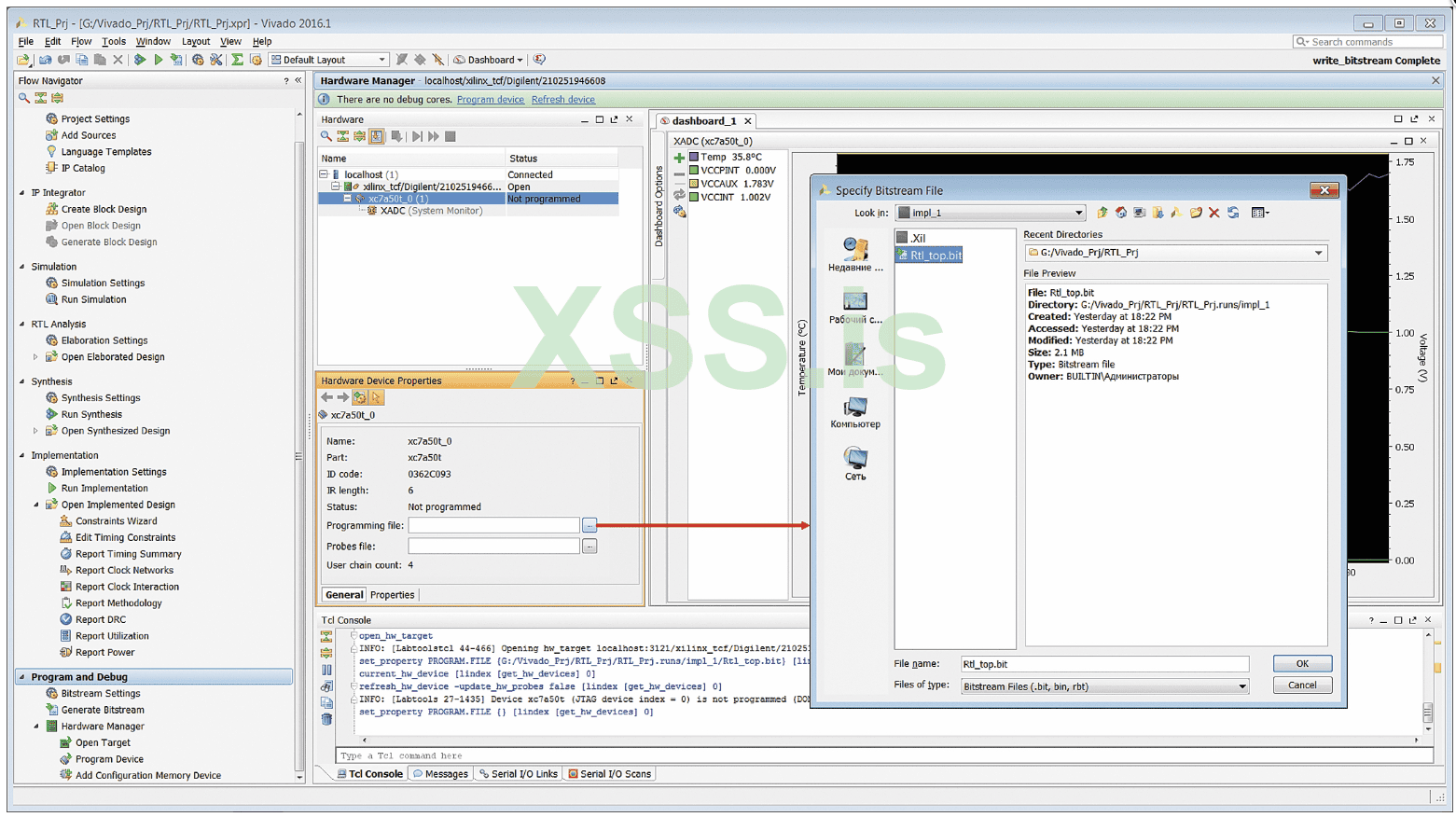

А все что выше семерки (тоже включая ее) - в софте Xilinx Vivado:

ПЛИС - довольно дорогие вещи, и работать с серией выше 7й, на этом форуме наверно может разве что LockBitSupp )

Virtex 7 стоит приблизительно 4000$, поэтому давайте остановимся на линейке FPGA до 7 серии включительно.

Как Вы уже поняли - использовать для разработки микропрограмм, мы будем Xilinx ISE. Самое последнее обновление данного IDE, датируется версией 14.7 - более новых версий нет и не будет, т.к. Xilinx имеет довольно жесткую политику - пересаживает всех пользователей на новый Vivado, заставляя при этом отказываться от использования старых чипов (и использовать новые более дорогие).

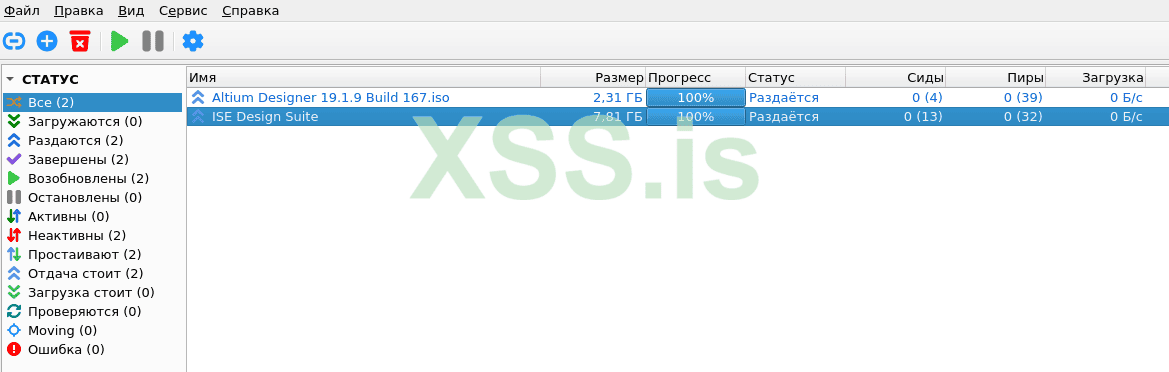

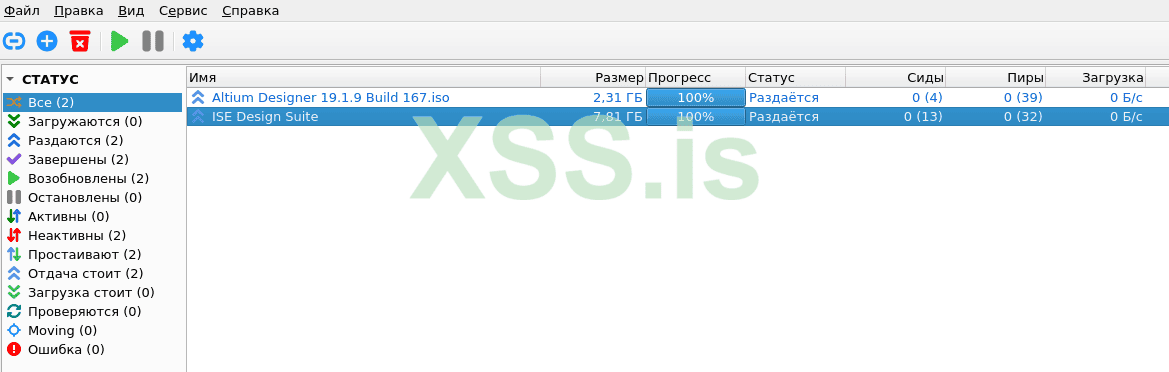

Я являюсь сторонником свободно распространяемого программного обеспечения, поэтому мы не станем покупать оригинальный IDE за 3500$, а просто скачаем его взломанную версию с торрентов ) .

Качаем проверенный мною (вся малварь работает как положено, отстук норм) торрент с дистрибутивом:

magnet:?xt=urn:btih:45be5fb83692627473a331fa13d6afbef84b8b5d&dn=ISE%20Design%20Suite&tr=http%3a%2f%2fbt2.t-ru.org%2fann%3fmagnet

Из архива извлекаем файлы Xilinx ISE Design Suite_14.7_1015_1.iso и xilinx_ise.lic , сам же архив ставим на раздачу следующим поколениям любителей открытого ПО.

Мы не ищем легких путей, и ставить будем IDE на Линукс! Почему так? Ну, во-первых - Linux Rulez, windows must die!

Мы не ищем легких путей, и ставить будем IDE на Линукс! Почему так? Ну, во-первых - Linux Rulez, windows must die!

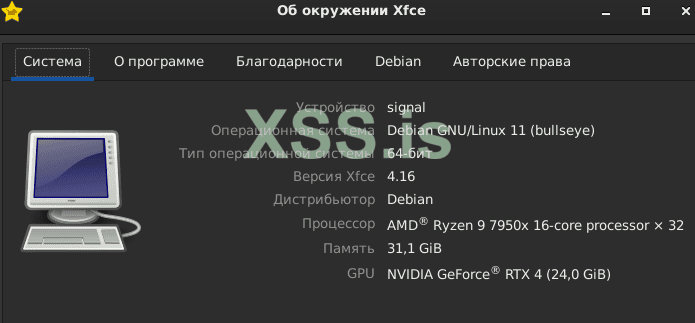

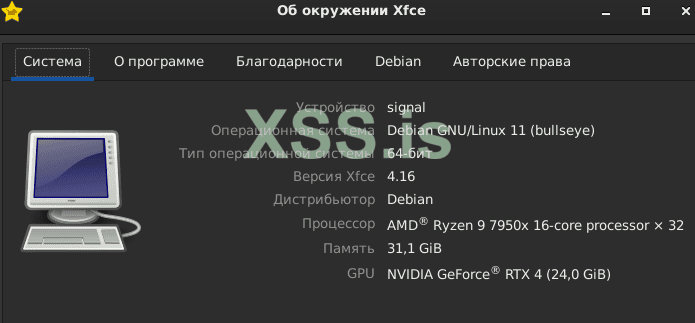

Во вторых - в работе с ПЛИС есть очень неприятный момент - это длительность "компиляции" прошивки. Т.е. вот Вы написали код, но прежде чем его загрузить в чип при помощи программатора - нужно собрать его в бинарник. Этот процесс длительный. ОЧЕНЬ длительный. Один из моих проектов, где используются 8 штук 7х Virtex'ов, компилируется 4 (!!!) суток на компьютере с Ryzen 7950x.

Я провел сравнение скорости и стабильности работы ISE под Win7 и Debian, разница - 10% увеличения скорости компиляции на линуксе. Это очень существенная величина, т.к. при отладке - иногда приходится пересобирать код десятки раз, и эти 10% в итоге выливаются в дни и недели сэкономленного времени.

Используем Debian 11, X-сервер XFCE.

Важный момент - софт придется ставить на основную машину, из под virtualbox или vmware программатор не заработает - уже неоднократно проверено.

Некоторые команды могут выполняться с ошибкой, т.к. пишу по памяти - но общий смысл такой. Если что-то не получается, пишите, будем исправлять и дорабатывать мануал вместе.

Монтируем Xilinx ISE Design Suite_14.7_1015_1.iso:

sudo mount -o loop Xilinx\ ISE\ Design\ Suite_14.7_1015_1.iso /mnt/iso

cd /mnt/iso

Запускаем ./xsetup (без использования привелегий суперпользователя, sudo)

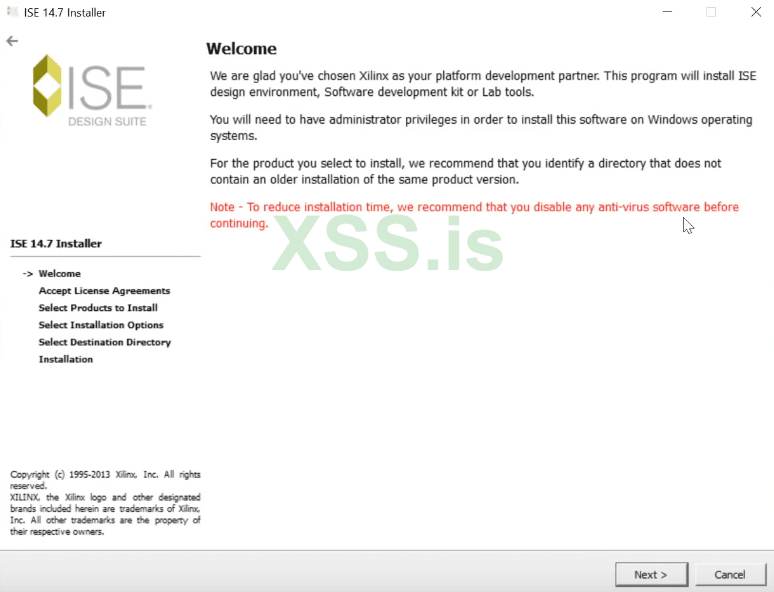

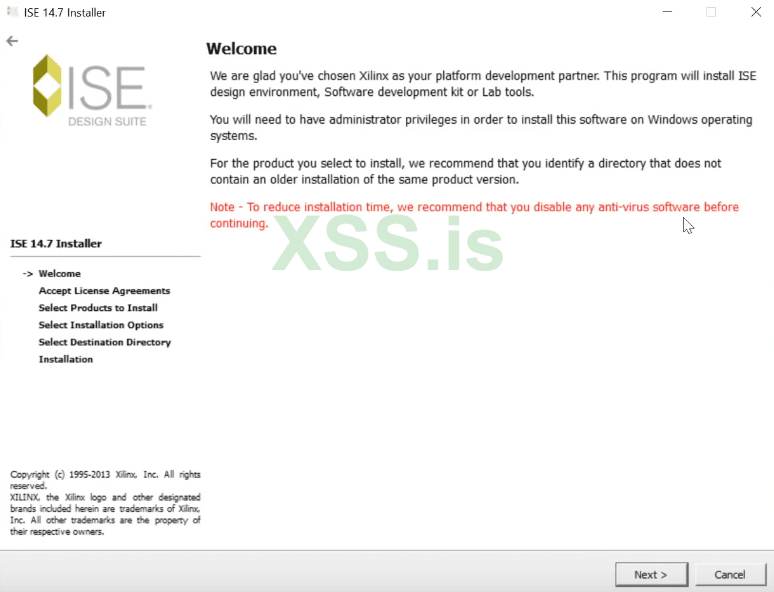

Открывается GUI инсталлятора:

Отключаем антивирус. Жмем Next >

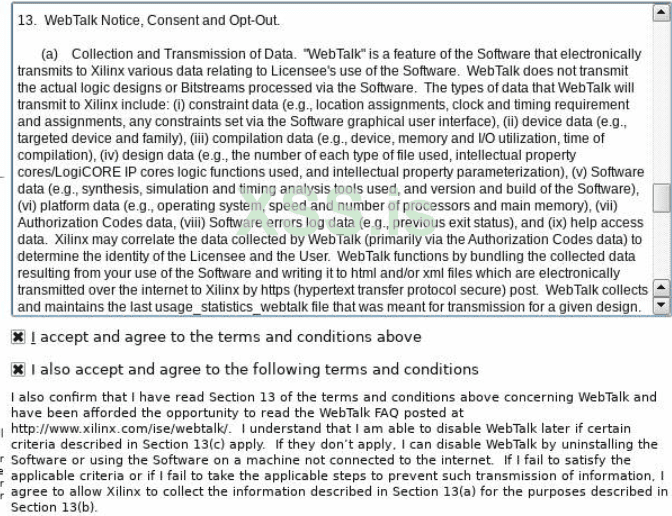

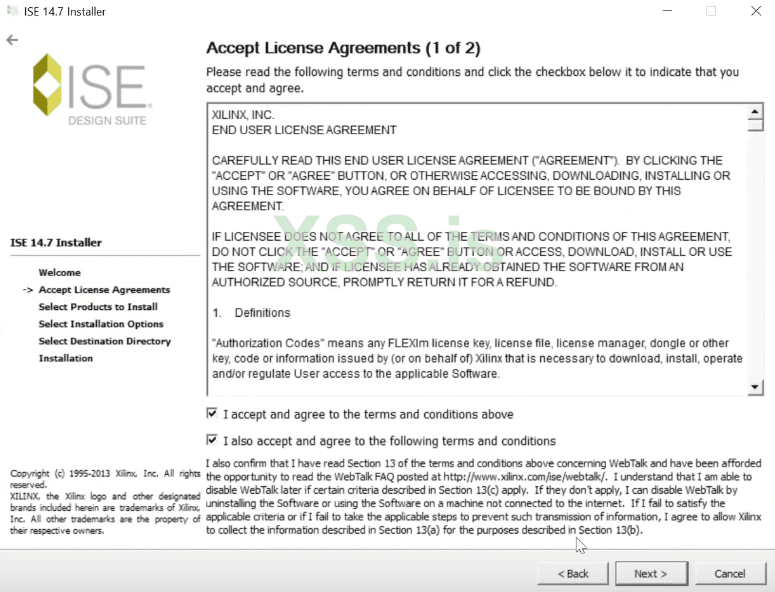

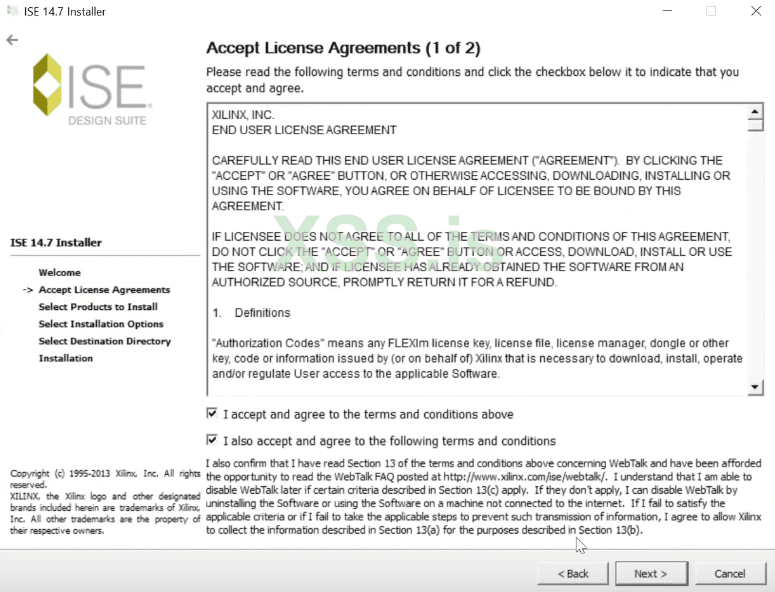

Ставим галочки и соглашаемся с тем что Xilinx оформит на вас 2 кредита.

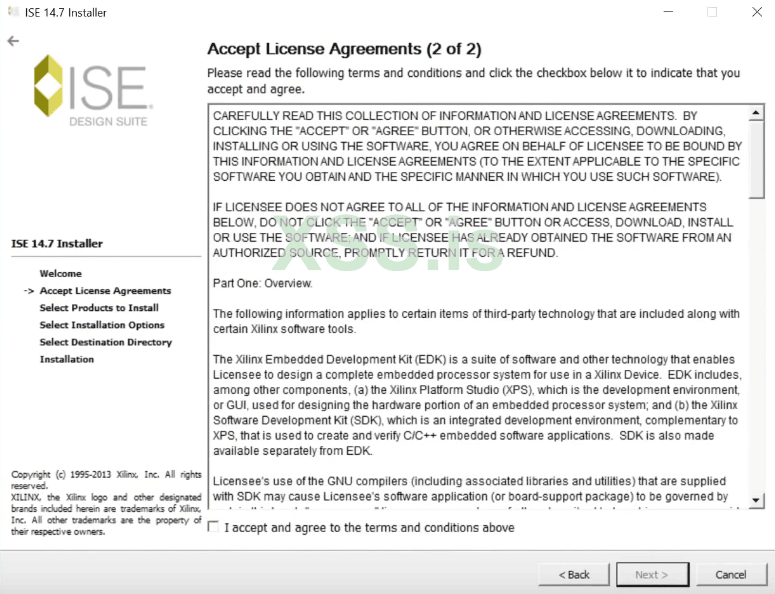

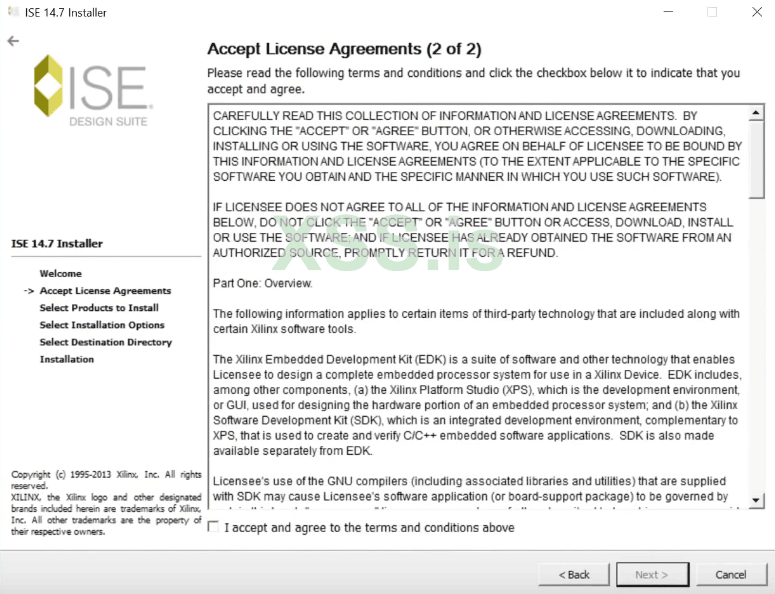

И еще одну галочку - разрешение на просмотр содержимого вашего HDD.

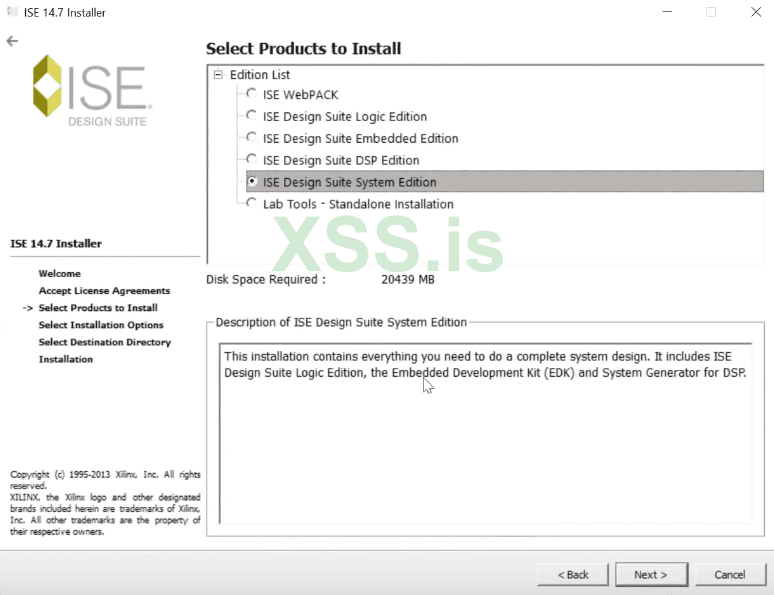

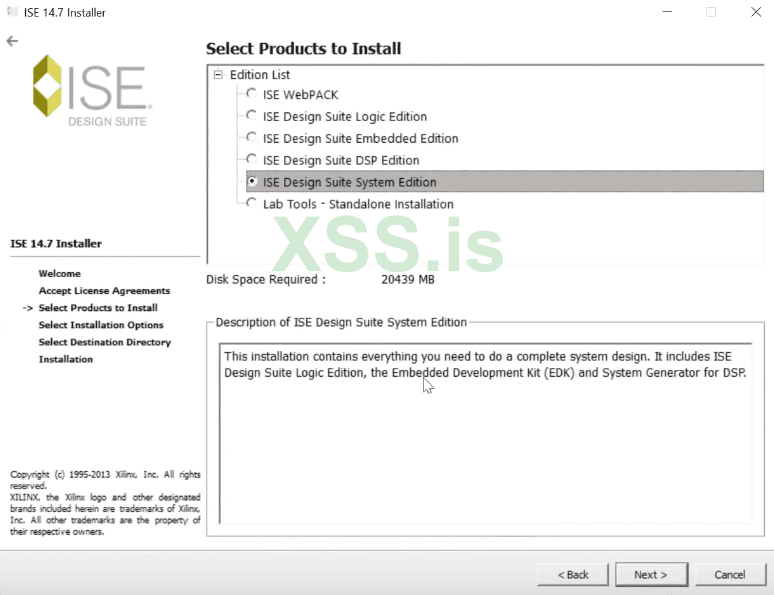

Тут нужно выбрать Suite System Edition - это наиболее полная установка, включающая в себя все платные модули и IP ядра.

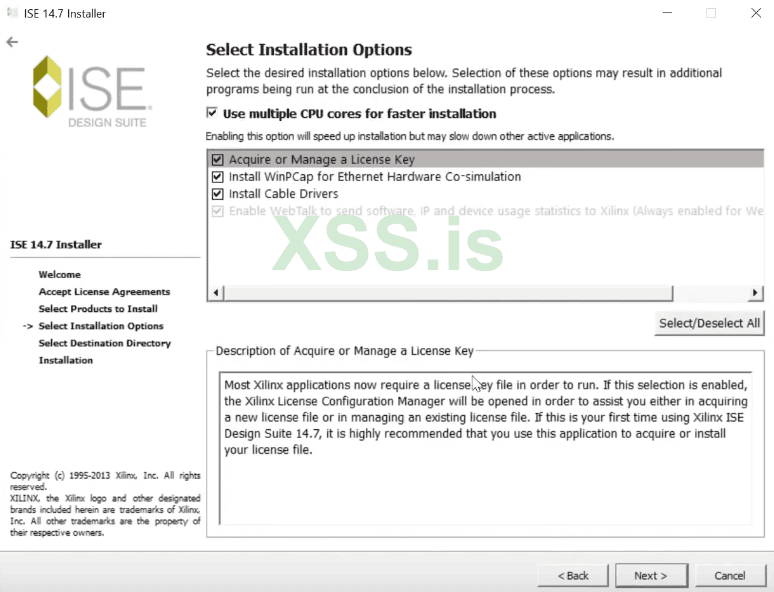

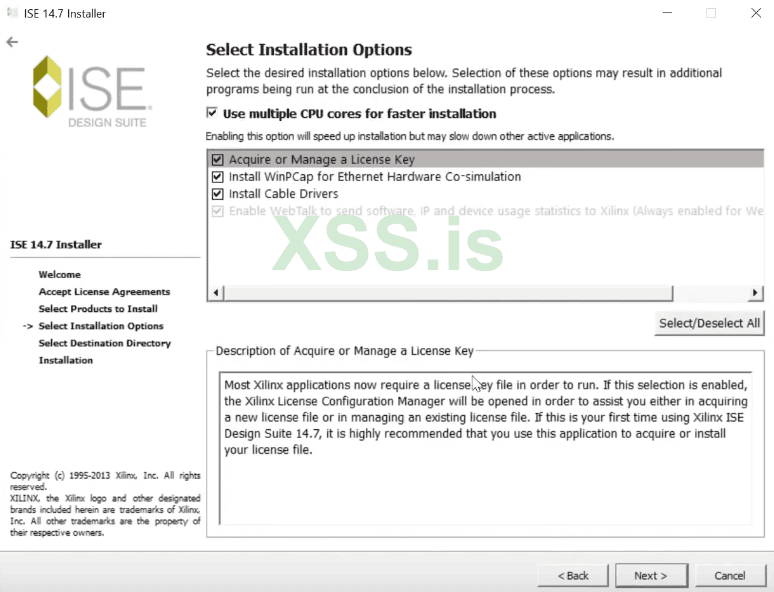

ОБЯЗАТЕЛЬНО снимаем галочку "Install Cable Drivers". ^^^^ Иначе страшные глюки ждут вас )

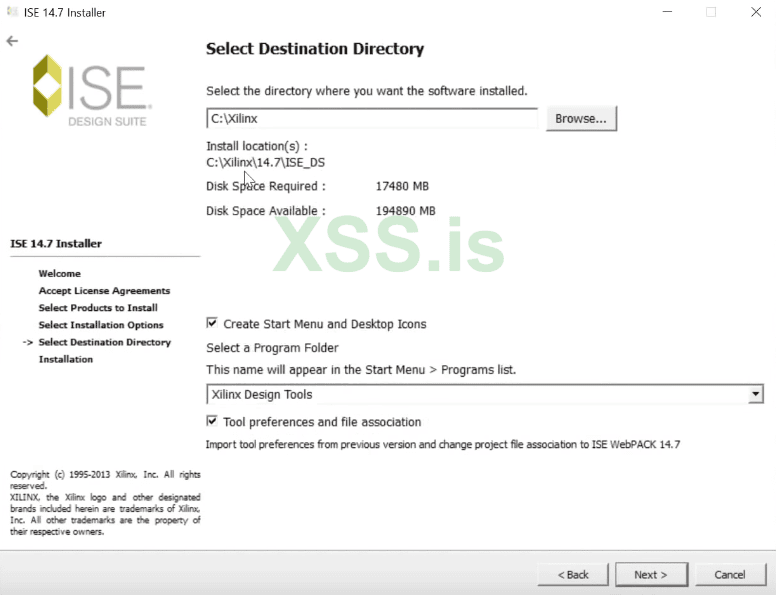

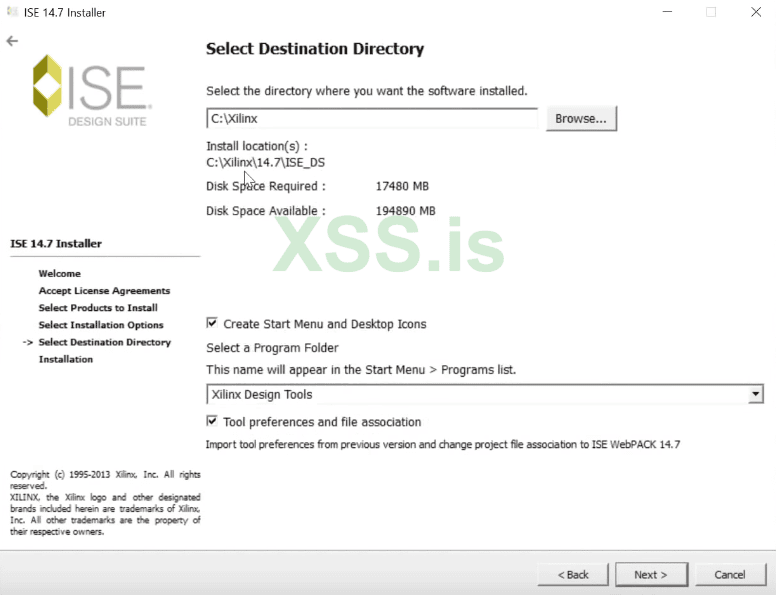

Путь установки - выбираем

/home/user/Xilinx

где "user" - соответственно ваша домашняя папка

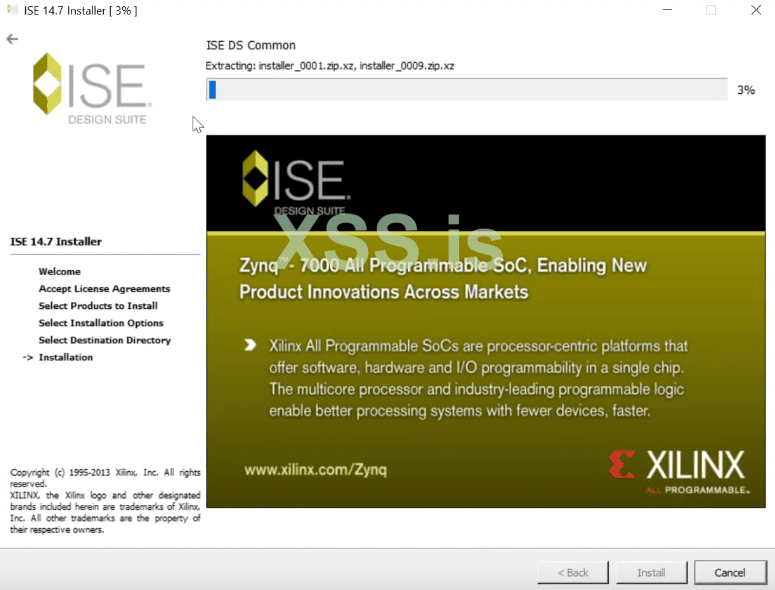

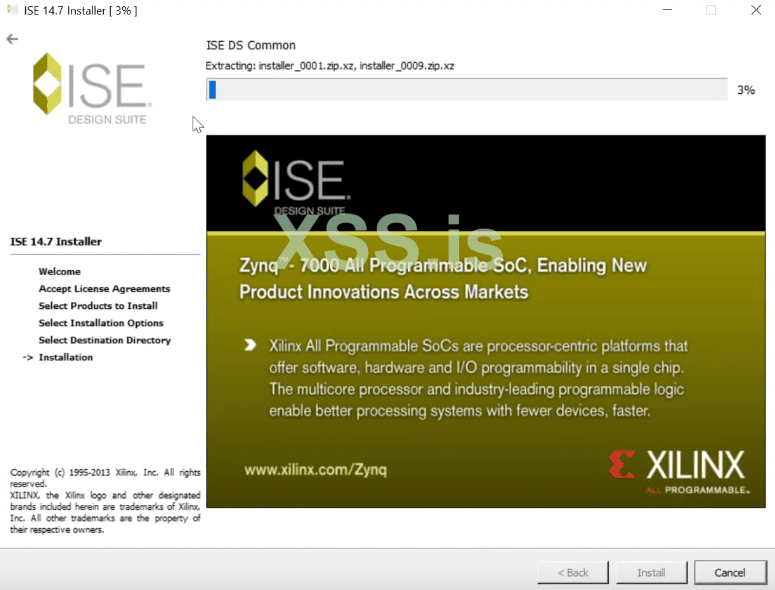

Процесс установки довольно долгий, занимает 10-15 минут.

После завершения установки, открываем файл

/home/user/.bashrc

и в самый конец добавляем строки

export PATH=$PATH:/home/user/Xilinx/14.7/ISE_DS/ISE/bin/lin64/

export PATH=$PATH:/home/user/Xilinx/14.7/ISE_DS/common/bin/lin64/

export XIL_IMPACT_USE_LIBUSB=1

Перезагружаемся.

Находим на локальном диске библиотеку libQt_Network.so . Копируем ее в каталоги. Можно создать символьные ссылки, но лучше скопировать.

/usr/lib/x86_64-linux-gnu/

/home/user/Xilinx/14.7/ISE_DS/ISE/lib/lin/

/home/user/Xilinx/14.7/ISE_DS/ISE/lib/lin64/

/home/user/Xilinx/14.7/ISE_DS/common/bin/lin64/

переходим в папку

cd /usr/lib/x86_64-linux-gnu/

Выполняем в ней команду

/sbin/ldconfig

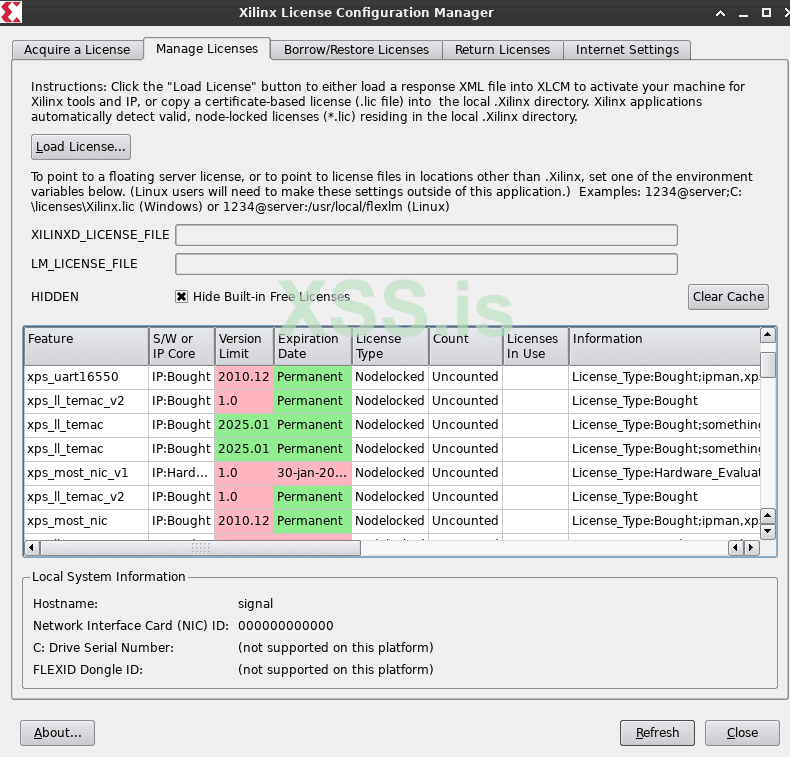

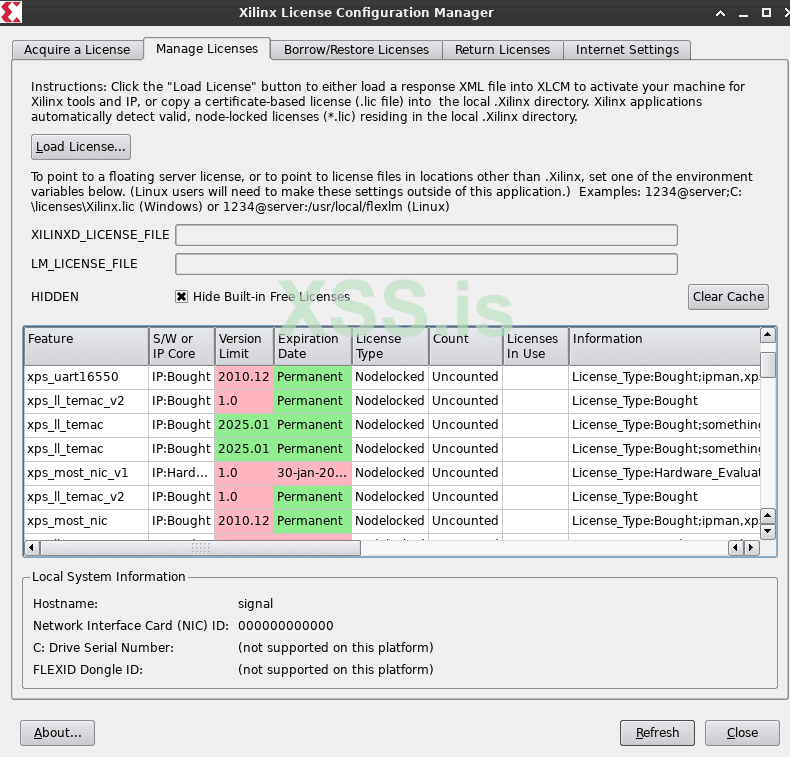

Запускаем Xilinx License manager командой

xlcm

Открываем вкладку Manage Licenses, нажимаем Load License, добавляем файл лицензии скачанный из торрента - xilinx_ise.lic

Проверяем, что ISE запускается командой из терминала

ise

При запуске не должен ругаться на лицензию.

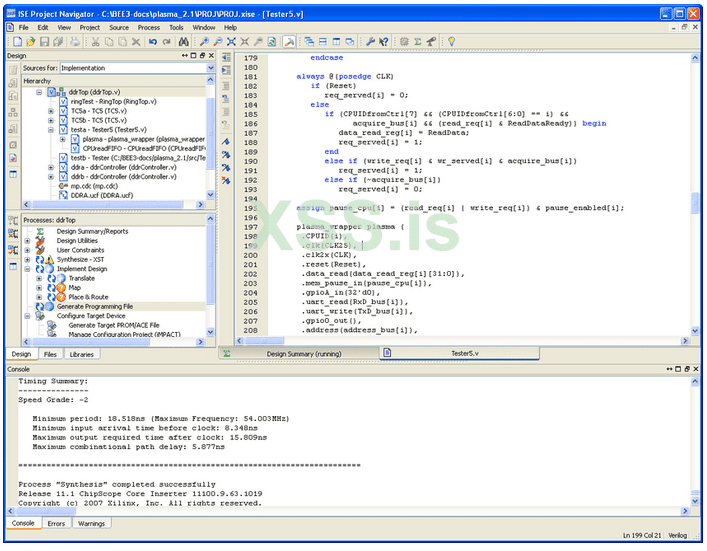

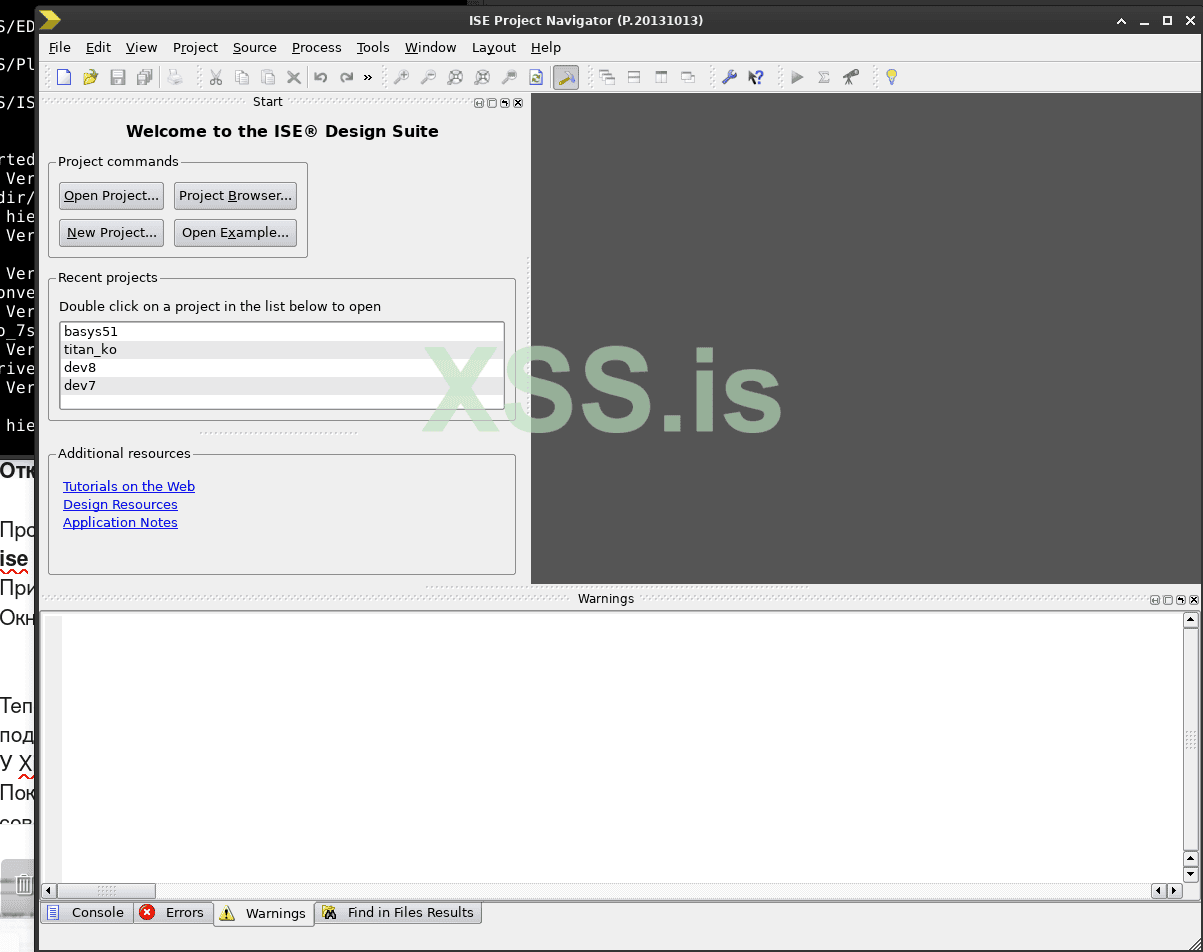

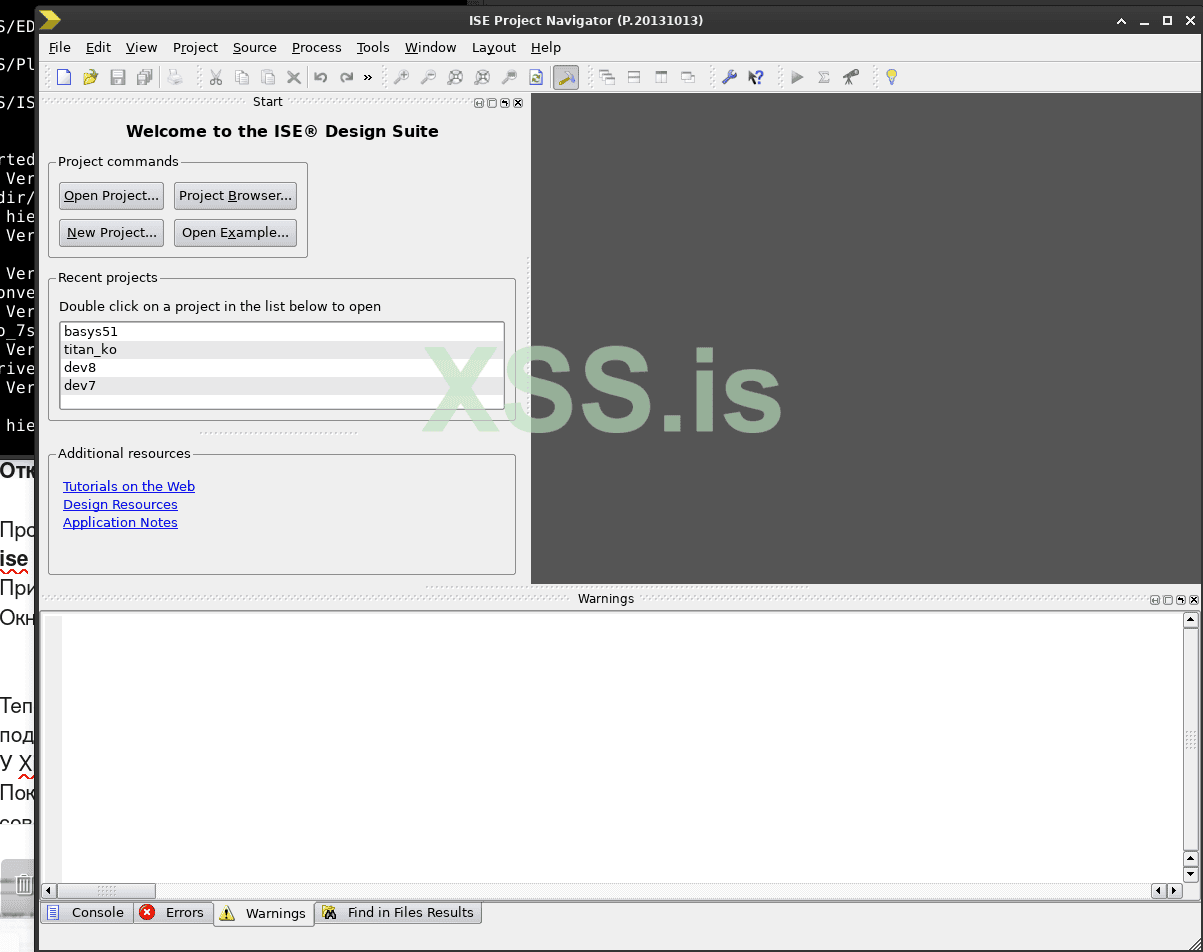

Окно будет выглядеть примерно так:

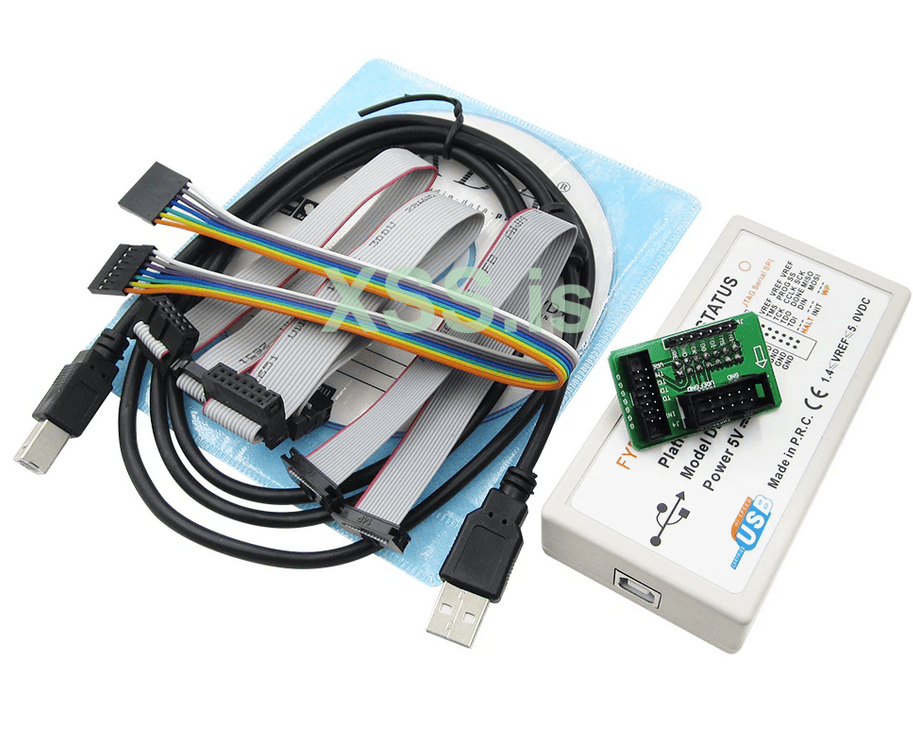

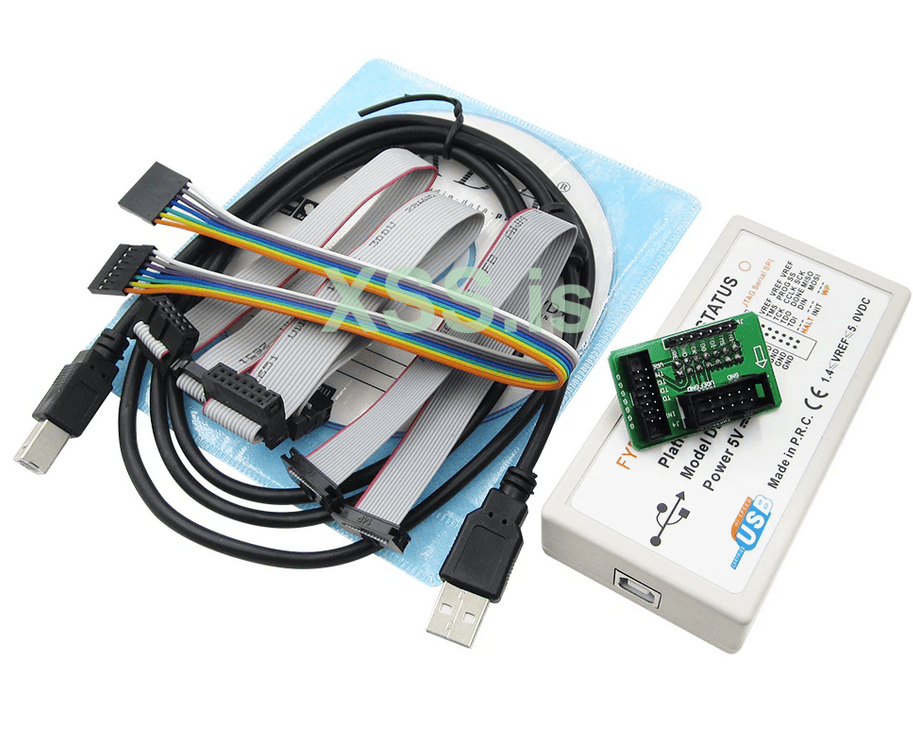

Теперь немного о программаторе. Для прошивки и отладки программного обеспечения в режиме JTAG, используются специальные адаптеры, подключаемые к ПЛИСу через 6и проводной интерфейс, а к компьютеру - через привычный USB.

У Xilinx'а есть несколько разновидностей устройства, все они называются Xilinx Platform Cable. Коробочка бывает белого цвета или красного.

Покупать нужно красный кабель, так как он USB 2.0, что существенно ускоряет процесс загрузки прошивок в ПЛИС. Китайский - категорически не советую, лучше использовать оригинальный Xilinx, он не очень дорогой.

Пример ПРАВИЛЬНОГО адаптера. Покупать нужно такой:

Примеры тех, которые ПОКУПАТЬ НЕЛЬЗЯ:

Ставим драйвера под него.

sudo apt-get install fxload libusb-1.0-0 libusb-1.0-0-dev

cd /home/user/Xilinx/14.7/ISE_DS/ISE/bin/lin64/

sudo cp *.hex /usr/share

sudo cp xusbdfwu.rules /etc/udev/rules.d

sudo sed -i -e 's/TEMPNODE/tempnode/' -e 's/SYSFS/ATTRS/g' -e 's/BUS/SUBSYSTEMS/' /etc/udev/rules.d/xusbdfwu.rules

Перезагружаемся

Подключаем Platform Cable в USB. Должна загореться красная индикаторная лампочка - это значит что драйвера встали нормально и система увидела программатор.

Если лампочка не загорелась - все пропало.

ISE все еще не сможет работать с адаптером, поэтому:

Находим файл libusb-0.1.so.4.4.4 (если нет то нужно установить старый libusb 0.1.4 )

Копируем этот файл, переименовав его в libusb.so в папки

/home/user/Xilinx/ISE_DS/ISE/lib/lin/

и

/home/user/Xilinx/ISE_DS/ISE/lib/lin64/

Убедившись что программатор подключен к USB, на нем горит красная лампочка - запускаем софт для загрузки прошивок, выполнив в консоле команду

impact

В процессе запуска производим наблюдение за состоянием светоизлучающего диода на корпусе программатора.

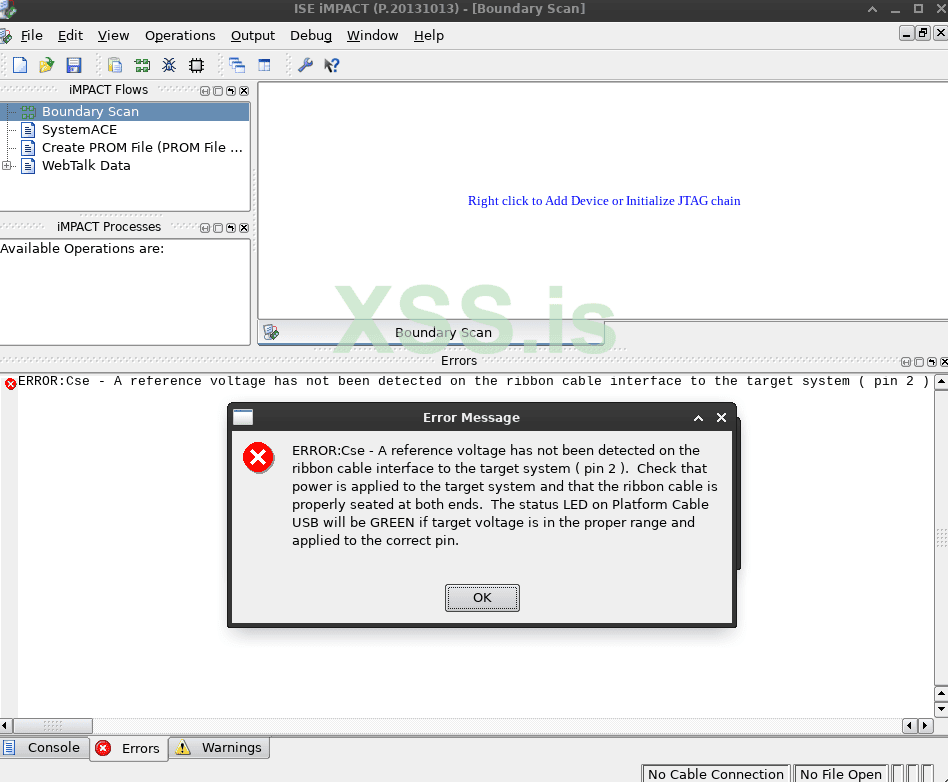

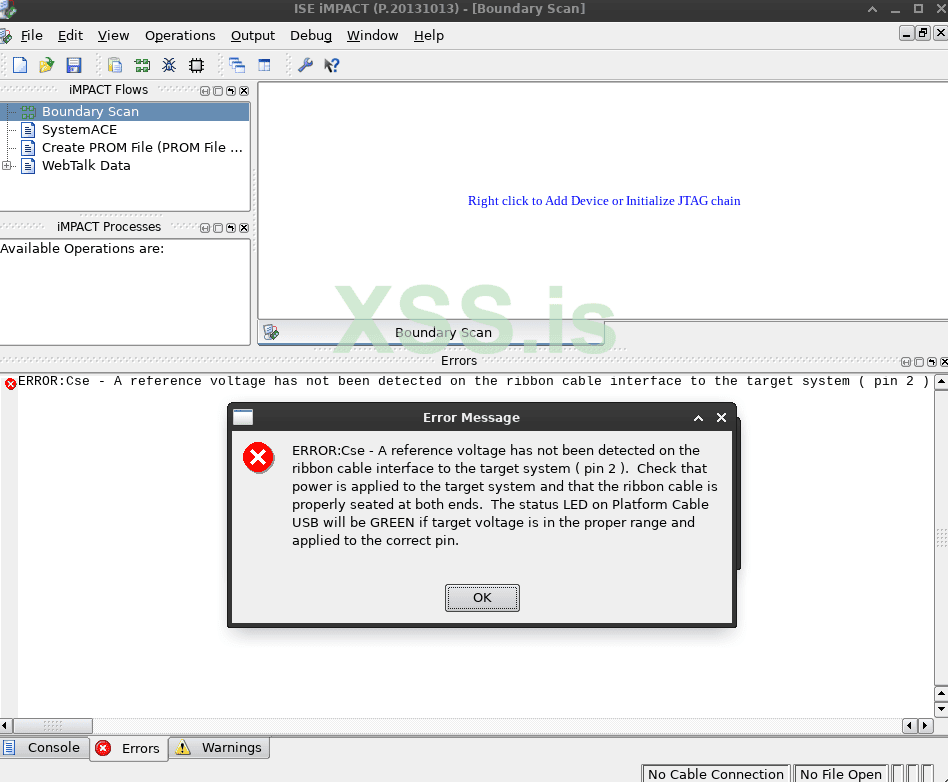

Диод должен мигнуть, после чего impact в окне с отладочной информацией напишет что то типа "voltage error". Это означает что он обнаружил программатор, но не определяет наличие напряжения питания на прошиваемой ПЛИСине, что логично - она же не подключена, интерфейс программатора висит в воздухе и питания на нем нет.

Если вы видите ошибку "reference voltage has not been detected" - программатор заработал!

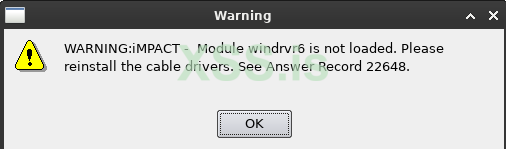

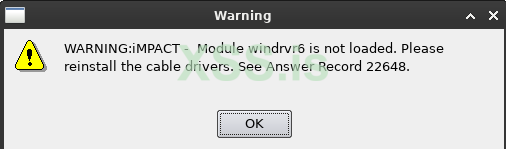

Ошибка драйвера windrvr6 является нормой - impact не может найти древние виндовые драйвера для программатора на LPT порт, как его отучить от этой дурной затеи - не знаю. Короче, ошибка ни на что не влияет, но имеет место быть:

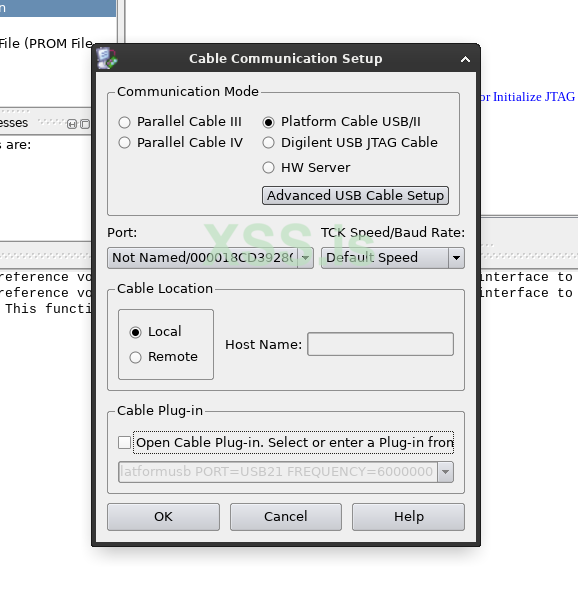

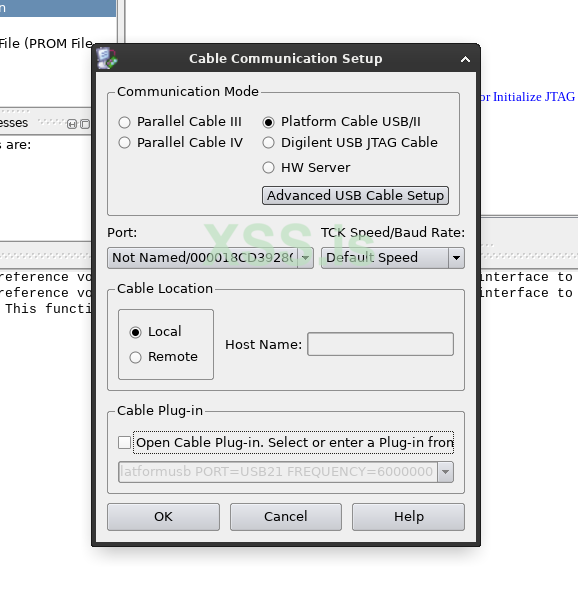

Можно зайти в настройки (правая кнопка мыши - "cable setup...") и перепроверить, должен быть включен режим Platform Cable USB II:

Работа с IP ядрами. IP - это не Internet Protocol, забудьте эту чушь - кто вам такое вообще сказал?

IP = Intellectual Property, интеллектуальная собственность. Кусочки чужого скомпилированного кода, которые Вы будете покупать за тысячи долларов и использовать в своих проектах, экономя при этом время на разработку.

Для работы с IP-ядрами используется модуль ISE COREGEN, который конечно же просто так под линуксом "не взлетит".

После установки он не может создать новые IP ядра - при нажатии кнопки generate выдает сообщение Unable to evaluate Tcl file. Данная проблема связана с тем что в ISE зачем-то есть 2 версии JAVA, старая и новая. Поэтому:

в папке ISE_DS/ISE/

mv java java.old

ln -sf java6 java

это решает проблему работы генератора ip ядер COREGEN.

Некоторые ядра такие как Clock Generator (очень часто используются) имеют свой GUI для их конфигурации, требуют английскую локаль. Но если ее включить глобально для всей системы, то в debian 11 перестает работать русская раскладка клавиатуры (слетают шрифты в консолях). Честно сказать я не разбирался в чем причина проблемы, и сделал проще. Создаем для ISE такой ярлык на рабочем столе:

[Desktop Entry]

Type=Application

Name=Xilinx ISE

Exec=env LC_ALL="en_US.UTF8" /home/user/Xilinx/14.7/ISE_DS/ISE/bin/lin64/ise

Icon=/home/user/Xilinx/14.7/ISE_DS/ISE/data/images/pn-ise.png

Terminal=false

Categories=Development;Engineering;Electronics;

Keywords=embedded electronics;electronics;fpga;xilinx;ise;spartan;virtex;

Запускать ise нужно при помощи этого ярлыка, а COREGEN запускать уже изнутри ISE через соответствующее меню.

Следующая особенность - при использовании модулей встраиваемых процессоров MicroBlaze, gui в программе Xilinx Platform Studio отрисовывается не полностью. Поэтому в /home/user/.bashrc добавляем строки

export PATH=$PATH:/home/user/Xilinx/14.7/ISE_DS/EDK/bin/lin64/

source /home/user/Xilinx/14.7/ISE_DS/settings64.sh

дальше удаляем старые библиотеки с которыми XPS работать не умеет:

mkdir Xilinx/14.7/ISE_DS/ISE/lib/lin64/bak

mv Xilinx/14.7/ISE_DS/ISE/lib/lin64/libstdc++* /opt/Xilinx/14.7/ISE_DS/ISE/lib/lin64/bak/

sudo mkdir Xilinx/14.7/ISE_DS/common/lib/lin64/bak

sudo mv Xilinx/14.7/ISE_DS/common/lib/lin64/libstdc++* /opt/Xilinx/14.7/ISE_DS/common/lib/lin64/bak/

Теперь edk/xps работают. Но при попытке скомпилировать прошивку МикроБлейза, вы испытаете эпик фейл - дело в том что среда разработки под MicroBlaze, это урезанный и модицифированный Eclipse, использующие старые библиотеки имеющие 32-х битную x86 архитектуру. Разумеется, на x64 оно не работает, поэтому

sudo apt-get install --yes lib32z1 lib32stdc++6

Последний на сегодня модуль, который пригодится в работе - chipscope (это как программный осциллограф - через интерфейс программатора можно заглянуть внутрь чипа и записать из него нужные сигналы). Для его работы под линуксом - нужно исправить файлы inserter и analyzer в каталоге /Xilinx/14.7/ISE_DS/ISE/bin/lin64/unwrapped. В заголовке файла меняем #!/bin/sh на #!/bin/bash

Начиная с установки среды разработки и заканчивая созданием простенького генератора хешей для взлома криптоалгоритма A5/1 используемого в GSM. Коснемся вопроса распараллеливания вычислений, отладки, работы с программаторами и методами загрузки прошивок.

К сожалению, некоторые материалы буду писать не в строгой идеологической последовательности, т.к. не всегда есть возможность "выдернуть" какую-то железку или вирт.машину из основных проектов, но в первом сообщении (этом) позже появится список ссылок и оглавление, где материал можно будет повторить-почитать уже более последовательно.

Так же, здесь будет больше практики, нежели чем теории. Основной упор - именно на "хакерское" применение ПЛИС, т.е. для использования их в качестве сопроцессоров для ускорения взломов паролей и т.д.

Часть 1. Установка среды разработки (IDE). Рабочее место ПЛИСовода.

Для начала - давайте разберем один момент.

Основные названия - Spartan, Artix, Virtex, Kintex

Серии - 3, 4, 5, 6, 7 и так далее. Отдельно еще есть линейка UltraScale.

Каждой комбинации, например - Spartan 3, соответствует определенный "размер" чипа, количество логических ячеек. Например, Spartan3-100, содержит в себе 100 000 логических элементов. Virtex4-75 - 75000 лог ячеек, но при этом он сам по себе быстрее чем Spartan и логические элементы (LUT'ы) у него устроены более сложно, что позволяет запускать более сложный софт, но занимать при этом меньше емкости чипа. Так же чипы бывают в корпусах с разным количеством ножек, с наличием или отсутствием PowerPC ядер и так далее.

Прошу заметить, что тут я сильно упрощаю - так как обещал минимум теории.

Это принципиально важный момент, так как микропрограммы чипов например Virtex3, Kintex 5, Virtex 7 (т.е. все что до семерки, включая ее) - разрабатываются в устаревшем IDE Xilinx ISE:

А все что выше семерки (тоже включая ее) - в софте Xilinx Vivado:

ПЛИС - довольно дорогие вещи, и работать с серией выше 7й, на этом форуме наверно может разве что LockBitSupp )

Virtex 7 стоит приблизительно 4000$, поэтому давайте остановимся на линейке FPGA до 7 серии включительно.

Как Вы уже поняли - использовать для разработки микропрограмм, мы будем Xilinx ISE. Самое последнее обновление данного IDE, датируется версией 14.7 - более новых версий нет и не будет, т.к. Xilinx имеет довольно жесткую политику - пересаживает всех пользователей на новый Vivado, заставляя при этом отказываться от использования старых чипов (и использовать новые более дорогие).

Я являюсь сторонником свободно распространяемого программного обеспечения, поэтому мы не станем покупать оригинальный IDE за 3500$, а просто скачаем его взломанную версию с торрентов ) .

Качаем проверенный мною (

magnet:?xt=urn:btih:45be5fb83692627473a331fa13d6afbef84b8b5d&dn=ISE%20Design%20Suite&tr=http%3a%2f%2fbt2.t-ru.org%2fann%3fmagnet

Из архива извлекаем файлы Xilinx ISE Design Suite_14.7_1015_1.iso и xilinx_ise.lic , сам же архив ставим на раздачу следующим поколениям любителей открытого ПО.

Во вторых - в работе с ПЛИС есть очень неприятный момент - это длительность "компиляции" прошивки. Т.е. вот Вы написали код, но прежде чем его загрузить в чип при помощи программатора - нужно собрать его в бинарник. Этот процесс длительный. ОЧЕНЬ длительный. Один из моих проектов, где используются 8 штук 7х Virtex'ов, компилируется 4 (!!!) суток на компьютере с Ryzen 7950x.

Я провел сравнение скорости и стабильности работы ISE под Win7 и Debian, разница - 10% увеличения скорости компиляции на линуксе. Это очень существенная величина, т.к. при отладке - иногда приходится пересобирать код десятки раз, и эти 10% в итоге выливаются в дни и недели сэкономленного времени.

Используем Debian 11, X-сервер XFCE.

Важный момент - софт придется ставить на основную машину, из под virtualbox или vmware программатор не заработает - уже неоднократно проверено.

Некоторые команды могут выполняться с ошибкой, т.к. пишу по памяти - но общий смысл такой. Если что-то не получается, пишите, будем исправлять и дорабатывать мануал вместе.

Монтируем Xilinx ISE Design Suite_14.7_1015_1.iso:

sudo mount -o loop Xilinx\ ISE\ Design\ Suite_14.7_1015_1.iso /mnt/iso

cd /mnt/iso

Запускаем ./xsetup (без использования привелегий суперпользователя, sudo)

Открывается GUI инсталлятора:

Отключаем антивирус. Жмем Next >

Ставим галочки и соглашаемся с тем что Xilinx оформит на вас 2 кредита.

И еще одну галочку - разрешение на просмотр содержимого вашего HDD.

Тут нужно выбрать Suite System Edition - это наиболее полная установка, включающая в себя все платные модули и IP ядра.

ОБЯЗАТЕЛЬНО снимаем галочку "Install Cable Drivers". ^^^^ Иначе страшные глюки ждут вас )

Путь установки - выбираем

/home/user/Xilinx

где "user" - соответственно ваша домашняя папка

Процесс установки довольно долгий, занимает 10-15 минут.

После завершения установки, открываем файл

/home/user/.bashrc

и в самый конец добавляем строки

export PATH=$PATH:/home/user/Xilinx/14.7/ISE_DS/ISE/bin/lin64/

export PATH=$PATH:/home/user/Xilinx/14.7/ISE_DS/common/bin/lin64/

export XIL_IMPACT_USE_LIBUSB=1

Перезагружаемся.

Находим на локальном диске библиотеку libQt_Network.so . Копируем ее в каталоги. Можно создать символьные ссылки, но лучше скопировать.

/usr/lib/x86_64-linux-gnu/

/home/user/Xilinx/14.7/ISE_DS/ISE/lib/lin/

/home/user/Xilinx/14.7/ISE_DS/ISE/lib/lin64/

/home/user/Xilinx/14.7/ISE_DS/common/bin/lin64/

переходим в папку

cd /usr/lib/x86_64-linux-gnu/

Выполняем в ней команду

/sbin/ldconfig

Запускаем Xilinx License manager командой

xlcm

Открываем вкладку Manage Licenses, нажимаем Load License, добавляем файл лицензии скачанный из торрента - xilinx_ise.lic

Проверяем, что ISE запускается командой из терминала

ise

При запуске не должен ругаться на лицензию.

Окно будет выглядеть примерно так:

Теперь немного о программаторе. Для прошивки и отладки программного обеспечения в режиме JTAG, используются специальные адаптеры, подключаемые к ПЛИСу через 6и проводной интерфейс, а к компьютеру - через привычный USB.

У Xilinx'а есть несколько разновидностей устройства, все они называются Xilinx Platform Cable. Коробочка бывает белого цвета или красного.

Покупать нужно красный кабель, так как он USB 2.0, что существенно ускоряет процесс загрузки прошивок в ПЛИС. Китайский - категорически не советую, лучше использовать оригинальный Xilinx, он не очень дорогой.

Пример ПРАВИЛЬНОГО адаптера. Покупать нужно такой:

Примеры тех, которые ПОКУПАТЬ НЕЛЬЗЯ:

Ставим драйвера под него.

sudo apt-get install fxload libusb-1.0-0 libusb-1.0-0-dev

cd /home/user/Xilinx/14.7/ISE_DS/ISE/bin/lin64/

sudo cp *.hex /usr/share

sudo cp xusbdfwu.rules /etc/udev/rules.d

sudo sed -i -e 's/TEMPNODE/tempnode/' -e 's/SYSFS/ATTRS/g' -e 's/BUS/SUBSYSTEMS/' /etc/udev/rules.d/xusbdfwu.rules

Перезагружаемся

Подключаем Platform Cable в USB. Должна загореться красная индикаторная лампочка - это значит что драйвера встали нормально и система увидела программатор.

Если лампочка не загорелась - все пропало.

ISE все еще не сможет работать с адаптером, поэтому:

Находим файл libusb-0.1.so.4.4.4 (если нет то нужно установить старый libusb 0.1.4 )

Копируем этот файл, переименовав его в libusb.so в папки

/home/user/Xilinx/ISE_DS/ISE/lib/lin/

и

/home/user/Xilinx/ISE_DS/ISE/lib/lin64/

Убедившись что программатор подключен к USB, на нем горит красная лампочка - запускаем софт для загрузки прошивок, выполнив в консоле команду

impact

В процессе запуска производим наблюдение за состоянием светоизлучающего диода на корпусе программатора.

Диод должен мигнуть, после чего impact в окне с отладочной информацией напишет что то типа "voltage error". Это означает что он обнаружил программатор, но не определяет наличие напряжения питания на прошиваемой ПЛИСине, что логично - она же не подключена, интерфейс программатора висит в воздухе и питания на нем нет.

Если вы видите ошибку "reference voltage has not been detected" - программатор заработал!

Ошибка драйвера windrvr6 является нормой - impact не может найти древние виндовые драйвера для программатора на LPT порт, как его отучить от этой дурной затеи - не знаю. Короче, ошибка ни на что не влияет, но имеет место быть:

Можно зайти в настройки (правая кнопка мыши - "cable setup...") и перепроверить, должен быть включен режим Platform Cable USB II:

Работа с IP ядрами. IP - это не Internet Protocol, забудьте эту чушь - кто вам такое вообще сказал?

IP = Intellectual Property, интеллектуальная собственность. Кусочки чужого скомпилированного кода, которые Вы будете покупать за тысячи долларов и использовать в своих проектах, экономя при этом время на разработку.

Для работы с IP-ядрами используется модуль ISE COREGEN, который конечно же просто так под линуксом "не взлетит".

После установки он не может создать новые IP ядра - при нажатии кнопки generate выдает сообщение Unable to evaluate Tcl file. Данная проблема связана с тем что в ISE зачем-то есть 2 версии JAVA, старая и новая. Поэтому:

в папке ISE_DS/ISE/

mv java java.old

ln -sf java6 java

это решает проблему работы генератора ip ядер COREGEN.

Некоторые ядра такие как Clock Generator (очень часто используются) имеют свой GUI для их конфигурации, требуют английскую локаль. Но если ее включить глобально для всей системы, то в debian 11 перестает работать русская раскладка клавиатуры (слетают шрифты в консолях). Честно сказать я не разбирался в чем причина проблемы, и сделал проще. Создаем для ISE такой ярлык на рабочем столе:

[Desktop Entry]

Type=Application

Name=Xilinx ISE

Exec=env LC_ALL="en_US.UTF8" /home/user/Xilinx/14.7/ISE_DS/ISE/bin/lin64/ise

Icon=/home/user/Xilinx/14.7/ISE_DS/ISE/data/images/pn-ise.png

Terminal=false

Categories=Development;Engineering;Electronics;

Keywords=embedded electronics;electronics;fpga;xilinx;ise;spartan;virtex;

Запускать ise нужно при помощи этого ярлыка, а COREGEN запускать уже изнутри ISE через соответствующее меню.

Следующая особенность - при использовании модулей встраиваемых процессоров MicroBlaze, gui в программе Xilinx Platform Studio отрисовывается не полностью. Поэтому в /home/user/.bashrc добавляем строки

export PATH=$PATH:/home/user/Xilinx/14.7/ISE_DS/EDK/bin/lin64/

source /home/user/Xilinx/14.7/ISE_DS/settings64.sh

дальше удаляем старые библиотеки с которыми XPS работать не умеет:

mkdir Xilinx/14.7/ISE_DS/ISE/lib/lin64/bak

mv Xilinx/14.7/ISE_DS/ISE/lib/lin64/libstdc++* /opt/Xilinx/14.7/ISE_DS/ISE/lib/lin64/bak/

sudo mkdir Xilinx/14.7/ISE_DS/common/lib/lin64/bak

sudo mv Xilinx/14.7/ISE_DS/common/lib/lin64/libstdc++* /opt/Xilinx/14.7/ISE_DS/common/lib/lin64/bak/

Теперь edk/xps работают. Но при попытке скомпилировать прошивку МикроБлейза, вы испытаете эпик фейл - дело в том что среда разработки под MicroBlaze, это урезанный и модицифированный Eclipse, использующие старые библиотеки имеющие 32-х битную x86 архитектуру. Разумеется, на x64 оно не работает, поэтому

sudo apt-get install --yes lib32z1 lib32stdc++6

Последний на сегодня модуль, который пригодится в работе - chipscope (это как программный осциллограф - через интерфейс программатора можно заглянуть внутрь чипа и записать из него нужные сигналы). Для его работы под линуксом - нужно исправить файлы inserter и analyzer в каталоге /Xilinx/14.7/ISE_DS/ISE/bin/lin64/unwrapped. В заголовке файла меняем #!/bin/sh на #!/bin/bash

Последнее редактирование: