ОРИГИНАЛЬНАЯ СТАТЬЯ

ПЕРЕВЕДЕНО СПЕЦИАЛЬНО ДЛЯ xss.pro

$600 на SSD для Jolah Milovski ---> 0x5B1f2Ac9cF5616D9d7F1819d1519912e85eb5C09 для поднятия ноды ETHEREUM и тестов

В этой статье представлен обзор и история создания аппаратных троянов, включая сетевые списки, подготовку матриц, изображения с электронного микроскопа и тестирование схем. Кроме того, мы создадим собственный дизайн физической схемы аппаратного трояна, который будет проанализирован с помощью Klayout.

RTL Design vs Netlist

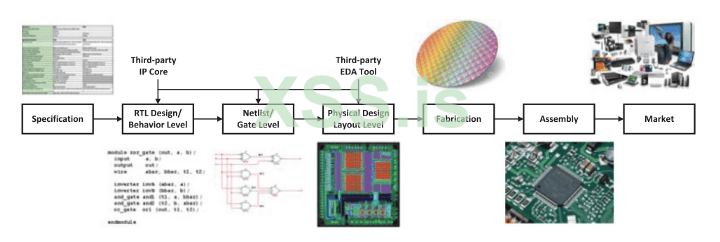

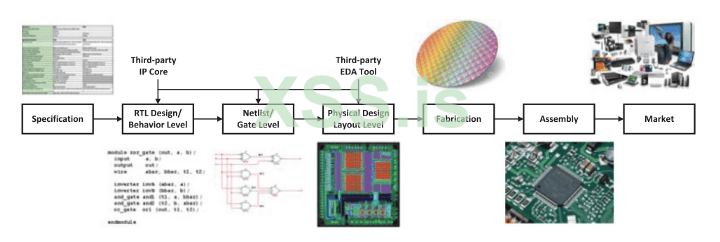

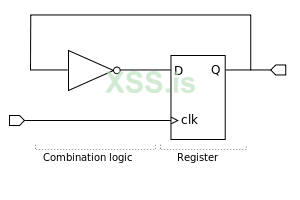

Прежде чем погрузиться в изучение аппаратных троянов, давайте рассмотрим, как проектируются кремниевые микросхемы, чтобы впоследствии мы могли обнаружить их с помощью обратной разработки. Мы можем начать с поведенческого уровня процесса. Регистровый уровень (RTL) определяет, как располагаются регистры и логические переходы.

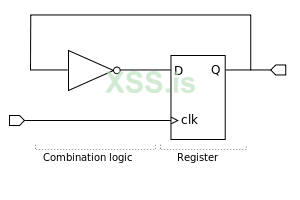

Схемотехника D-триггер

Схемотехника D-триггер

Проектирование RTL стало намного проще в 1983 году, когда Министерством обороны был разработан первый язык описания аппаратуры (HDL) для документирования поведения проектов интегральных схем, специфичных для конкретного приложения (ASIC). VHDL и Verilog были представлены примерно в то же время и до сих пор являются двумя наиболее популярными HDL. Эти языки были созданы как специализированный компьютерный язык для программирования цифровых логических схем. Если взять приведенную выше RTL-схему и преобразовать ее в код Verilog, она будет выглядеть следующим образом:

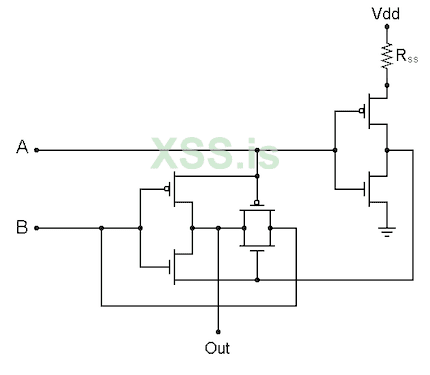

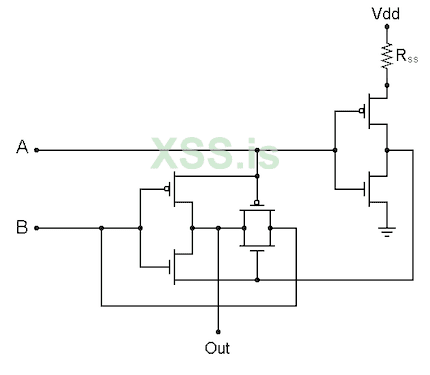

Этот простой фрагмент кода можно синтезировать для обсуждаемой конструкции логических соединений. Логический синтез — это автоматизированный процесс преобразования языка HDL, такого как Verilog или VHDL, в оптимизированное описание на уровне соединений. При обратном проектировании изображений кремниевых кристаллов первая цель — понять, как мы можем взять все эти слои и преобразовать их в список соединений транзисторов. Глядя на что-то вроде вентиля XOR с двумя входами без значков компонентов RTL для замены транзисторов, мы можем разработать эту схему:

Список соединений XOR Gate

Список соединений XOR Gate

Проще говоря, потребовалось всего шесть транзисторов, чтобы создать комплементарный дизайн списка соединений металл-оксид-полупроводник (CMOS). С этого момента в нашем путешествии по обратному проектированию вы должны преобразовать этот список соединений в схему RTL, а затем в HDL, как видно из изображений и фрагментов кода выше.

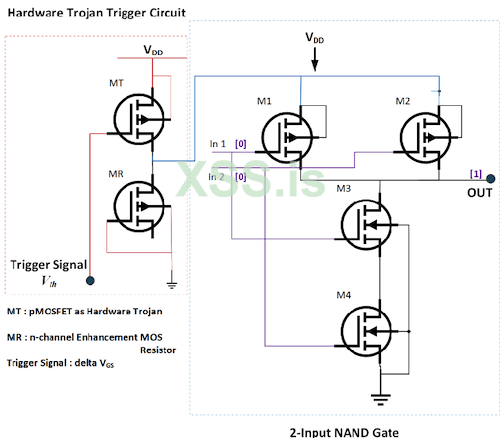

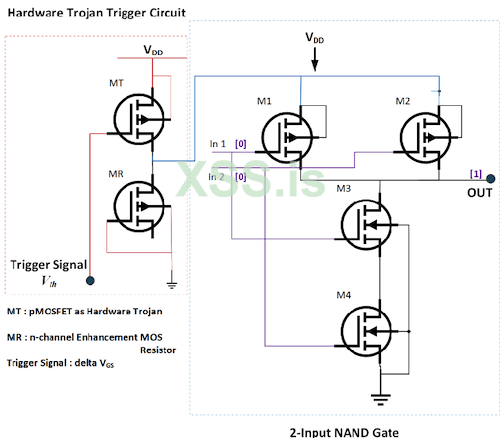

Согласно документу Ingress of Threshold Voltage Triggered Hardware Trojan in the Modern FPGA Fabric — Methodology Detection and Mitigation : основные цели проекта для HTVth установлены соответственно таким образом, что:

В этом примере злоумышленник может легко контролировать выход логического элемента И-НЕ с двумя входами. С A(1) NAND B(0) == AB(1), мы ожидаем ввода 1а также 0 для получения высокого напряжения на выходе. При вставленном трояне уравнение для A NAND Bбудет иметь противоположный предполагаемый результат. Триггер аппаратного троянца (HWT) может так же легко изменить определенные входные контакты или изменить ожидаемые результаты. Это может помочь получить доступ к встроенным учетным данным, ключам, коду и многому другому.

Вставка троянов

Есть много способов вставить троянов, потому что есть много разных типов троянов.Один тип имеет возможность размещать фиксированные входы, подающие на два триггера, таким образом, чтобы микросхема по-прежнему проходила встроенные проверки самотестирования (BIST). Это может упростить обход механизма безопасности отладки. Второй тип включает возможность сделать атаки по сторонним каналам более доступными. Третий тип, трояны на стадии макета, могут быть внедрены в нескольких точках, особенно если несколько сторонних IP-ядер объединены в одном проекте. В принципе, одна разработка может стать жертвой нескольких троянцев, созданных разными группами злоумышленников.

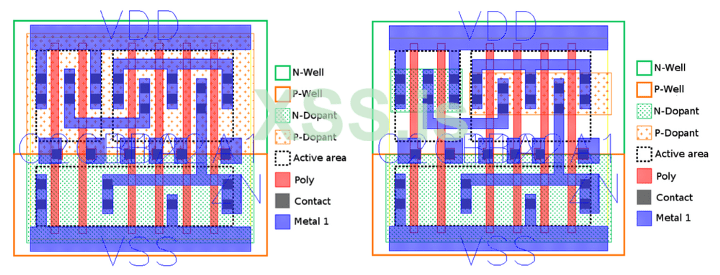

Вставка RTL — один из самых популярных способов внедрения аппаратных троянов. Сам троянец может быть объектом системного уровня, который преобразуется в мошеннический RTL или может быть доставлен во время компоновки ASIC. Кроме того, троянец может маскировать подготовку, изменяя данные, чтобы замаскировать схему, которая уже находится в производстве. Это достигается за счет использования технологий повышения разрешения ( RET ), таких как коррекция оптической близости ( OPC ), которая корректирует волнообразное поведение света при травлении наноразмерных атрибутов самых современных интегральных схем. Дополнительную информацию можно найти в Википедии на Tape-outs. Чередование маски может, например, изменить полярность легирующей примеси внутри транзистора, с n-типа на p-тип или наоборот. Исследователи из Института безопасности полупроводников Хорста Герца заявили, что это будет чрезвычайно сложно обнаружить, особенно если это будет сделано после подписания. Подделка, безусловно, может внести изменения непосредственно перед изготовлением маски.

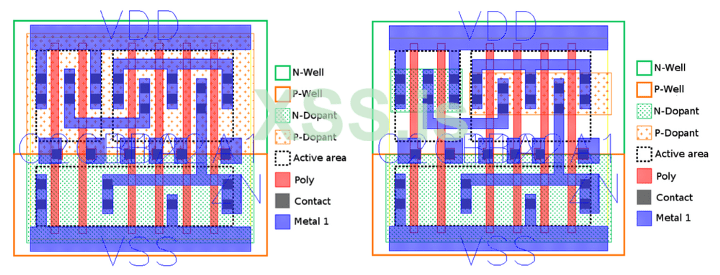

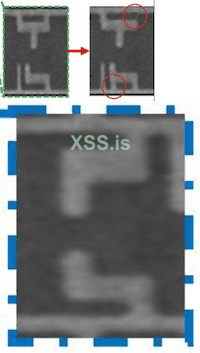

Измененный размер p-dopant, используемый для воздействия на поведение ячейки AOI

В приведенном выше случае, который был представлен Беккером и др, инвертор мог быть сфальсифицирован, чтобы обеспечить неправильный выходной сигнал. Например, Vdd может быть высоким в любое время за счет переключения маски p-примеси на версию n-типа или изменить его мощность за счет уменьшения ширины p-канального металлооксидно-полупроводникового (PMOS) транзистора. На изображении выше p-примесь охватывает всю область Vdd, но на схеме Trojan (справа) она занимает только более половины транзисторов на стороне Vdd. Трояны, способные воздействовать более чем на один путь, имеют больше шансов быть обнаруженными. При низкой вероятности перехода трояны вряд ли повлияют на энергопотребление схемы. Даже если сети выбираются из некритических путей без общих сегментов, обнаружить троянов с помощью методов, основанных на задержке, будет крайне сложно. Этот процесс тестирования был применен к схеме Ethernet MAC 10GE, и чип был синтезирован на технологическом узле 90 нм. Ему был поставлен троянец-компаратор, который следит за проводами шины данных. Логика компараторов, как показано ниже, переключается при изменении шины данных и поэтому потребляет значительное количество энергии.

Как видите, вставка троянов на уровне RTL или даже на уровне шлюза довольно сложна и может иметь много последствий, если не будет выполнена должным образом, например, значительное увеличение энергопотребления или ошибочное поведение. Было обнаружено, что анализ сигнала бокового канала и анализ вероятности перехода мощности показали самое высокое и наиболее точное количество цепей и вероятностей перехода из-за того, что он может показывать аномалии мощности, вызванные работой компараторов. Было показано, что это лучше, чем такие методы, как анализ задержки и структурный анализ (которые не обнаружили в схеме проверяемых неисправностей).

Если мы посмотрим на троянов с точки зрения макета, игра немного изменится. В большинстве случаев при проектировании схем есть много неиспользуемых пространств или даже областей, которые подвергаются химико-механической полировке (CMP). Троянские ячейки, размещенные в области, не используемой схемой, оказывают большее влияние на энергопотребление схемы, чем все остальные методы, перечисленные выше.

Был разработан поток для разделения схемы и определения практических мест для троянских ячеек, занимающих неиспользуемые места. Распределение ячеек схемы и пробелов по компоновке схемы получается, а затем определяются возможные места для размещения ячеек схемы.

Подготовка образцов, микроскопические изображения и тестирование

Использование методов обратного оптического проектирования может многое открыть исследователю. Обычные микроскопы, такие как составной, стерео- или даже металлургический, могут использоваться для обнаружения троянов, но отраслевой стандарт склоняется к сканирующим электронным микроскопам (СЭМ), поскольку ИС становятся меньше. Расширенные возможности необходимы для того, чтобы иметь возможность проводить дальнейшие исследования. Чтобы даже подготовить чип для показа скрытых троянов, некоторые вещи делаются с легированием, что требует использования химического травителя.

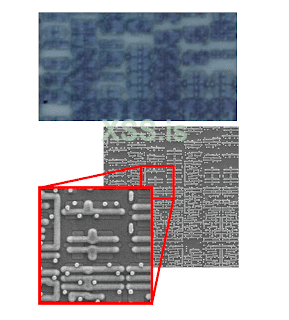

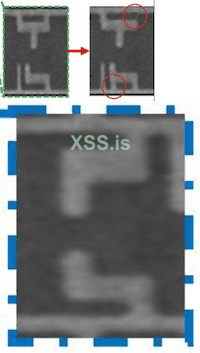

Как видно на увеличенном изображении ниже, затвор оригинальной конструкции (КМОП-инвертор) модифицирован путем применения другой полярности легирующей примеси к дискретным частям активной области затвора.

СЭМ-изображение троянца в 130-нм чипе (из книги «Современное состояние реверс-инжиниринга ИС»)

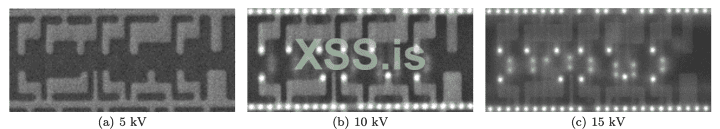

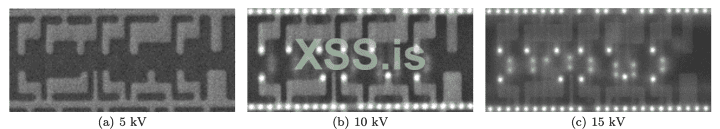

Согласно исследованию, проведенному Университетом Северной Каролины, они смогли зафиксировать мощность транзисторов на определенном значении и/или даже имели возможность изменять мощность транзисторов аналогичным образом. Университет Флориды провел аналогичное исследование по обнаружению троянов с использованием различных напряжений луча на специальном CMOS-чипе. Используя этот метод, они смогли использовать быстрые алгоритмы визуализации SEM, обработки изображений и компьютерного зрения для обнаружения изменений вставки, удаления и модификации между микросхемой, свободной от троянов, и IC, проходящей аутентификацию (IUA). Как обсуждалось выше, необходима подготовительная работа, чтобы подготовить чип к визуализации, поскольку электроны не могут проникнуть в толстый слой подложки из диоксида кремния (SiO₂). Обычно используемый метод удаления SiO₂ — механическая полировка, так как его легче контролировать, чем что-то вроде погружения стружки в плавиковую кислоту, как показано в моей последней статье. Для обеспечения равномерного утончения субстрата исследователи использовали VarioMill. Этот продукт использует лазерное химическое травление, пятиосную адаптивную микрообработку с ЧПУ и спектрометрию видимого/ИК-излучения для утончения задней стороны толщиной до 1 мкм. Цель здесь состоит в том, чтобы взять изображения SEM из IUA и сравнить их с золотым IC. Для SEM необходимо установить определенные параметры, чтобы получить эффективное изображение IUA, например, напряжение луча, поле зрения, время пребывания (скорость) и разрешение. С этими настройками микроскоп можно запрограммировать на отображение всей ИС.

Исследователи внесли изменения в уровень легирования, чтобы смоделировать активность троянца, который затем был получен с помощью РЭМ. В некоторых из этих примеров злоумышленник потенциально может заменить NAND на NOR, который, по сути, будет реализовывать собственную вредоносную логику с помощью таких методов, как модификация активной области, маскировка ячеек на 1-м металлическом слое или путем вставки/удаления логики на активной области (т.е. добавление инвертора).

Современные микроконтроллеры и ЦП имеют от 10 000 до миллиардов переходов, и для анализа потребуется множество изображений с микроскопа. Вот почему автоматизация играет ключевую роль, когда речь идет о сборе информации как о номинальных цепях, так и о цепях с троянами. Многообещающими оказались и другие проверенные методы, в частности тестирование задержки пути . В эксперименте Йеля исследователи вставили троянца на основе 2-битного компаратора рядом с входом ядра DES чипа. Задержки пути используются для создания отпечатков номинальных микросхем, поэтому каждый путь в списке соединений включается в состав трассы. Каждый отпечаток представляет собой один аспект общих характеристик подлинного дизайна. Затем чипы проверяются путем сравнения их параметров задержки пути с отпечатками пальцев, что довольно важно, когда речь идет о крошечных троянских схемах. В конечном итоге они смогли сделать вывод, что подлинными будут считаться только те чипы, чьи точки выборки находятся на пересечении всех заданных наборов во всем пространстве отпечатков пальцев или рядом с ним. Если одно или несколько мест выборки находились далеко от указанного пересечения, то считалось, что в чип вставлен троянец.

Теперь мы рассмотрим раздел, в котором аппаратный троян создается с помощью инструментов Electronic Design Automation (EDA) с открытым исходным кодом, чтобы показать, как он выглядит на уровне нестандартного дизайна.

ASIC Дизайн собственного HWT

Теперь, когда у нас была возможность узнать об аппаратных троянцах из множества разных источников, я подумал, что было бы интересно создать свой собственный от RTL до GDSII, где мы могли бы фактически просматривать наш чип с помощью программного обеспечения для 3D-рендеринга, такого как GDS3D. Прелесть разработки нашего собственного зараженного чипа заключается в том, что мы можем увидеть, как использовать инструменты с открытым исходным кодом для этого, а также иметь возможность смотреть на интегральную схему без микроскопа, поскольку мы можем увеличивать столько, сколько захотим, с помощью программного обеспечения. Давайте рассмотрим схему на уровне затвора обычной логической схемы И-ИЛИ с 4 входами рядом с той же схемой, но со вставленным трояном. Мы преобразуем это в код Verilog, а затем используем либо QFlow с OSU PDK, либо Openlane на Skywater130 PDK для создания файлов GDSII, чтобы мы могли просмотреть дизайн ASIC, как если бы мы смотрели на него через объектив с увеличением.

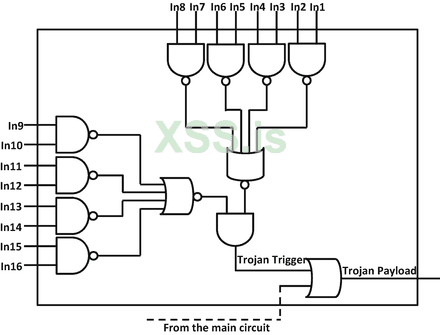

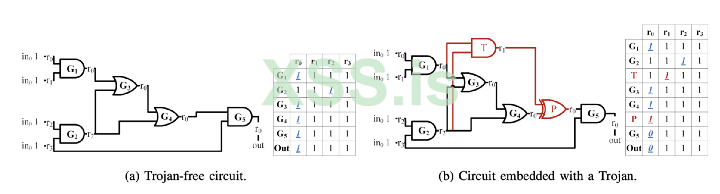

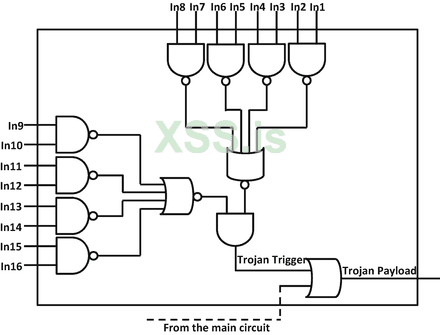

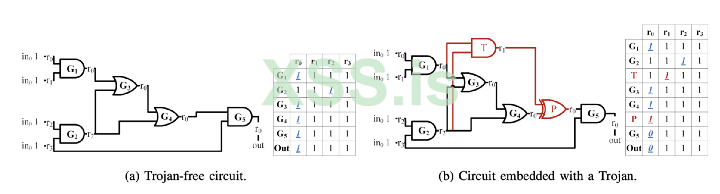

По словам Димитриса Моуриса, Шарля Гуэрта и Нектариоса Георгиоса Цуцоса, ворота помечаются порядком оценки (первый G1, тогда G2, так далее.). Трассировка выполнения также показана в строках таблиц, которые будут отображать выходные данные четырех регистров конечного автомата (SM), которые определяются переменными r0 — r3. Выделенные и подчеркнутые значения в таблицах показывают, какая переменная моделирования была перезаписана после оценки логического элемента. На диаграмме (а) показана схема, которая выводит 1когда все четыре входа установлены на высокий уровень. На диаграмме (б) показана та же схема, что и (а), после внедрения примера троянца, который активируется только тогда, когда все входы установлены на 1.

У нас есть два способа преобразования логики уровня шлюза в Verilog: либо вручную, либо с помощью цифрового инструмента . Мы можем нарисовать схемы и преобразовать программное обеспечение в HDL по нашему выбору. Я выберу более ленивый вариант Б.

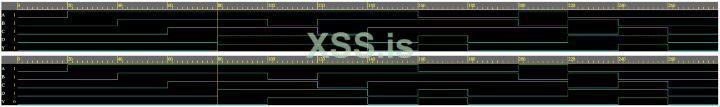

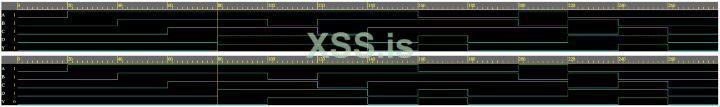

Это довольно похоже на код без троянца, за исключением того, что этот код имеет операцию XOR вместе с дополнительным И с вводом C& D. Мы можем использовать EDA Playground для имитации волновых моделей, используя простой тестовый стенд для обоих. Если вы не знакомы с написанием тестовых стендов, вы можете посмотреть мой код , чтобы увидеть, как они написаны. По сути, мы проверяем входные данные A, B, C, & Dчтобы увидеть, как трудно было бы заметить разницу с точки зрения формы волны. Помните, что наша кривая должна показывать активацию трояна только тогда, когда у нас есть 4'b1111, все остальные входные и выходные сигналы должны отражать друг друга.

Если вы посмотрите на эту простую конструкцию ИС, она разбита на несколько простых логических вентилей. Первый из них - AOI21X1, это инверторный затвор AND-OR с 3 входами, который имеет функцию Y=!((A&B)|C).

При снятии слоев наша конструкция соответствует функции AOI и содержит 6 транзисторов PNP и NPN. Если сравнить эту конструкцию с конструкцией AOI21X1 во вставленном проекте HWT, то они выглядят совершенно одинаково. На самом деле обе конструкции содержат BUFX2 (неинвертирующий буфер [Y=A]), INVX1 (инвертор [Y=!A]) и NAND2X1 (двухвходовой NAND-затвор [Y=!(A&B)]). Давайте посмотрим, какие стандартные ячейки добавил наш зараженный дизайн.

Как мы видим, это не так незаметно, как это было на уровне RTL-симуляции или даже вставки троянов на уровне легирования, потому что теперь кажется, что есть еще пара затворов. Наш дизайн показывает, что дополнительная ячейка, которая была добавлена, была NAND3X1 рядом с оригинальной NAND2X1. Кроме того, рядом с неинвертирующим буфером был добавлен дополнительный 2-входовой NAND-гейт.

С левой стороны у нас есть 4 транзистора, составляющие наш 2-входовой NAND-затвор, а выход Y этого затвора подключен к входу A вставленного 3-входового NAND-затвора (с правой стороны), который влияет на выход этого затвора. Этот дополнительный затвор состоит из 6 транзисторов, что в общей сложности составляет дополнительные 10 транзисторов к зараженной конструкции ИС. Так где же все это соединяется, чтобы повлиять на фактический физический выходной вывод?

Добавляя слои обратно, мы видим, что верхний металлический (зеленый) слой показывает два физических вывода, вход D и выход Y. Дополнительные два NAND-затвора, вставленные в эту конструкцию, в конечном итоге изменят выход этого вывода, когда будет установлен определенный триггер, что в нашем случае означает, что все физические входные выводы установлены в 1. Сравнивая наш код Verilog с дизайном ИС, можно увидеть сходство между ними и то, почему было бы так трудно уловить их на некоторых этапах предварительной сборки. Мы можем взглянуть на 3D-модель, чтобы увидеть, как это будет выглядеть на пластине.

Если бы не дополнительные заполнители (две большие пустые оранжевые и желтые области), которые были автоматически размещены и маршрутизированы с помощью QFlow в нижней части конструкции HWT, они выглядели бы почти идентично, поскольку два дополнительных затвора, о которых говорилось ранее, не добавляют многого к конструкции.

Вам может быть интересно, в каком сценарии это будет вредоносно, отличный вопрос. Представьте, что эти четыре входных контакта, когда все они установлены в состояние HIGH, ожидают результата в виде выхода HIGH, который, по сути, позволяет микросхеме заблокировать процессор в состоянии без отладки. После того, как наша атака изменит конструкцию, она убедится, что когда все контакты установлены в положение HIGH, на выходе будет LOW. Это переведет процессор в состояние отладки, что позволит злоумышленникам или противникам узнать частную информацию и IP вашей SoC (System on Chip), которая не должна была стать общедоступной.

Заключение

В этой статье мы рассмотрели некоторые способы внедрения троянских программ, рассмотрели методы их обнаружения и разработали собственную программу с нуля, используя имеющиеся в моем распоряжении инструменты. Благодаря этому исследованию мы можем реально увидеть, как будет выглядеть зараженный чип со стороны цепочки поставок.

ВОТ репозиторий, содержащий все HDL и файлы проектирования, которые я создал на этапе исследования размещения и маршрутизации моей аппаратной троянской микросхемы.

Спасибо, что следили за мной! Надеюсь, вам понравилось так же, как и мне. Если у вас есть вопросы по этой статье, пожалуйста, напишите мне в Instagram: @hackersclub или Twitter: @ringoware

Счастливой охоты

ПЕРЕВЕДЕНО СПЕЦИАЛЬНО ДЛЯ xss.pro

$600 на SSD для Jolah Milovski ---> 0x5B1f2Ac9cF5616D9d7F1819d1519912e85eb5C09 для поднятия ноды ETHEREUM и тестов

Введение

В то время как индустрия безопасности обычно фокусируется на программных кибератаках, мы не можем забывать о влиянии на безопасность аппаратных недостатков более низкого уровня, таких как те, которые затрагивают полупроводники. Поверхность для атак на уровне кремния за последние несколько лет расширилась; по мере развития производства интегральных схем (ИС) для все более совершенной микроэлектроники также возрастает риск появления дефектов в этих сложных системах.

В этой статье представлен обзор и история создания аппаратных троянов, включая сетевые списки, подготовку матриц, изображения с электронного микроскопа и тестирование схем. Кроме того, мы создадим собственный дизайн физической схемы аппаратного трояна, который будет проанализирован с помощью Klayout.

RTL Design vs Netlist

Прежде чем погрузиться в изучение аппаратных троянов, давайте рассмотрим, как проектируются кремниевые микросхемы, чтобы впоследствии мы могли обнаружить их с помощью обратной разработки. Мы можем начать с поведенческого уровня процесса. Регистровый уровень (RTL) определяет, как располагаются регистры и логические переходы.

Проектирование RTL стало намного проще в 1983 году, когда Министерством обороны был разработан первый язык описания аппаратуры (HDL) для документирования поведения проектов интегральных схем, специфичных для конкретного приложения (ASIC). VHDL и Verilog были представлены примерно в то же время и до сих пор являются двумя наиболее популярными HDL. Эти языки были созданы как специализированный компьютерный язык для программирования цифровых логических схем. Если взять приведенную выше RTL-схему и преобразовать ее в код Verilog, она будет выглядеть следующим образом:

Код:

lways @(posedge clk)

begin

Q <= D;

end

assign D = ~Q;Этот простой фрагмент кода можно синтезировать для обсуждаемой конструкции логических соединений. Логический синтез — это автоматизированный процесс преобразования языка HDL, такого как Verilog или VHDL, в оптимизированное описание на уровне соединений. При обратном проектировании изображений кремниевых кристаллов первая цель — понять, как мы можем взять все эти слои и преобразовать их в список соединений транзисторов. Глядя на что-то вроде вентиля XOR с двумя входами без значков компонентов RTL для замены транзисторов, мы можем разработать эту схему:

Проще говоря, потребовалось всего шесть транзисторов, чтобы создать комплементарный дизайн списка соединений металл-оксид-полупроводник (CMOS). С этого момента в нашем путешествии по обратному проектированию вы должны преобразовать этот список соединений в схему RTL, а затем в HDL, как видно из изображений и фрагментов кода выше.

Получение изображений кремниевых кристаллов

Чтобы обнаружить аппаратных троянов, вам нужно иметь под рукой голый кристалл вместе с несколькими другими приготовлениями к чипу, о которых я расскажу позже в этом посте. Одна часть, которую я не буду касаться, — это процесс декапсуляции и задержки интегральных схем, поскольку я уже написал статью об этом, но необходимо понять, как получить эти крошечные кремниевые кристаллы и как они отображаются.Определение аппаратных троянов

Аппаратный троянец может иметь вид вредоносной схемы, нарушающей работу или надежность электронной системы (например, интегральной схемы). Схемы подвержены атакам этого типа на уровне физической схемы или на уровне ворот. В частности, трояны уровня шлюза представляют собой функциональные модификации или параметрические отклонения от предполагаемого назначения компонента и могут быть достигнуты путем добавления или удаления шлюзов. Трудно обнаруживаемые трояны могут использоваться для ослабления защиты криптопроцессора следующими способами:- Уменьшение эффективной энтропии генератора случайных чисел

- Выдача злоумышленнику информации о внутренней работе процессора.

Согласно документу Ingress of Threshold Voltage Triggered Hardware Trojan in the Modern FPGA Fabric — Methodology Detection and Mitigation : основные цели проекта для HTVth установлены соответственно таким образом, что:

- Задача передачи троянской схемы должна быть линейной.

- Чувствительность к изменениям температуры и порогового напряжения должна быть очень высокой.

- Изменение на выходе должно быть достаточно большим для изменения на входе.

- Должны сохраняться незначительная временная деградация и устойчивость к изменениям процесса.

В этом примере злоумышленник может легко контролировать выход логического элемента И-НЕ с двумя входами. С A(1) NAND B(0) == AB(1), мы ожидаем ввода 1а также 0 для получения высокого напряжения на выходе. При вставленном трояне уравнение для A NAND Bбудет иметь противоположный предполагаемый результат. Триггер аппаратного троянца (HWT) может так же легко изменить определенные входные контакты или изменить ожидаемые результаты. Это может помочь получить доступ к встроенным учетным данным, ключам, коду и многому другому.

Вставка троянов

Есть много способов вставить троянов, потому что есть много разных типов троянов.Один тип имеет возможность размещать фиксированные входы, подающие на два триггера, таким образом, чтобы микросхема по-прежнему проходила встроенные проверки самотестирования (BIST). Это может упростить обход механизма безопасности отладки. Второй тип включает возможность сделать атаки по сторонним каналам более доступными. Третий тип, трояны на стадии макета, могут быть внедрены в нескольких точках, особенно если несколько сторонних IP-ядер объединены в одном проекте. В принципе, одна разработка может стать жертвой нескольких троянцев, созданных разными группами злоумышленников.

Вставка RTL — один из самых популярных способов внедрения аппаратных троянов. Сам троянец может быть объектом системного уровня, который преобразуется в мошеннический RTL или может быть доставлен во время компоновки ASIC. Кроме того, троянец может маскировать подготовку, изменяя данные, чтобы замаскировать схему, которая уже находится в производстве. Это достигается за счет использования технологий повышения разрешения ( RET ), таких как коррекция оптической близости ( OPC ), которая корректирует волнообразное поведение света при травлении наноразмерных атрибутов самых современных интегральных схем. Дополнительную информацию можно найти в Википедии на Tape-outs. Чередование маски может, например, изменить полярность легирующей примеси внутри транзистора, с n-типа на p-тип или наоборот. Исследователи из Института безопасности полупроводников Хорста Герца заявили, что это будет чрезвычайно сложно обнаружить, особенно если это будет сделано после подписания. Подделка, безусловно, может внести изменения непосредственно перед изготовлением маски.

Измененный размер p-dopant, используемый для воздействия на поведение ячейки AOI

В приведенном выше случае, который был представлен Беккером и др, инвертор мог быть сфальсифицирован, чтобы обеспечить неправильный выходной сигнал. Например, Vdd может быть высоким в любое время за счет переключения маски p-примеси на версию n-типа или изменить его мощность за счет уменьшения ширины p-канального металлооксидно-полупроводникового (PMOS) транзистора. На изображении выше p-примесь охватывает всю область Vdd, но на схеме Trojan (справа) она занимает только более половины транзисторов на стороне Vdd. Трояны, способные воздействовать более чем на один путь, имеют больше шансов быть обнаруженными. При низкой вероятности перехода трояны вряд ли повлияют на энергопотребление схемы. Даже если сети выбираются из некритических путей без общих сегментов, обнаружить троянов с помощью методов, основанных на задержке, будет крайне сложно. Этот процесс тестирования был применен к схеме Ethernet MAC 10GE, и чип был синтезирован на технологическом узле 90 нм. Ему был поставлен троянец-компаратор, который следит за проводами шины данных. Логика компараторов, как показано ниже, переключается при изменении шины данных и поэтому потребляет значительное количество энергии.

Как видите, вставка троянов на уровне RTL или даже на уровне шлюза довольно сложна и может иметь много последствий, если не будет выполнена должным образом, например, значительное увеличение энергопотребления или ошибочное поведение. Было обнаружено, что анализ сигнала бокового канала и анализ вероятности перехода мощности показали самое высокое и наиболее точное количество цепей и вероятностей перехода из-за того, что он может показывать аномалии мощности, вызванные работой компараторов. Было показано, что это лучше, чем такие методы, как анализ задержки и структурный анализ (которые не обнаружили в схеме проверяемых неисправностей).

Если мы посмотрим на троянов с точки зрения макета, игра немного изменится. В большинстве случаев при проектировании схем есть много неиспользуемых пространств или даже областей, которые подвергаются химико-механической полировке (CMP). Троянские ячейки, размещенные в области, не используемой схемой, оказывают большее влияние на энергопотребление схемы, чем все остальные методы, перечисленные выше.

Был разработан поток для разделения схемы и определения практических мест для троянских ячеек, занимающих неиспользуемые места. Распределение ячеек схемы и пробелов по компоновке схемы получается, а затем определяются возможные места для размещения ячеек схемы.

Подготовка образцов, микроскопические изображения и тестирование

Использование методов обратного оптического проектирования может многое открыть исследователю. Обычные микроскопы, такие как составной, стерео- или даже металлургический, могут использоваться для обнаружения троянов, но отраслевой стандарт склоняется к сканирующим электронным микроскопам (СЭМ), поскольку ИС становятся меньше. Расширенные возможности необходимы для того, чтобы иметь возможность проводить дальнейшие исследования. Чтобы даже подготовить чип для показа скрытых троянов, некоторые вещи делаются с легированием, что требует использования химического травителя.

Как видно на увеличенном изображении ниже, затвор оригинальной конструкции (КМОП-инвертор) модифицирован путем применения другой полярности легирующей примеси к дискретным частям активной области затвора.

СЭМ-изображение троянца в 130-нм чипе (из книги «Современное состояние реверс-инжиниринга ИС»)

Согласно исследованию, проведенному Университетом Северной Каролины, они смогли зафиксировать мощность транзисторов на определенном значении и/или даже имели возможность изменять мощность транзисторов аналогичным образом. Университет Флориды провел аналогичное исследование по обнаружению троянов с использованием различных напряжений луча на специальном CMOS-чипе. Используя этот метод, они смогли использовать быстрые алгоритмы визуализации SEM, обработки изображений и компьютерного зрения для обнаружения изменений вставки, удаления и модификации между микросхемой, свободной от троянов, и IC, проходящей аутентификацию (IUA). Как обсуждалось выше, необходима подготовительная работа, чтобы подготовить чип к визуализации, поскольку электроны не могут проникнуть в толстый слой подложки из диоксида кремния (SiO₂). Обычно используемый метод удаления SiO₂ — механическая полировка, так как его легче контролировать, чем что-то вроде погружения стружки в плавиковую кислоту, как показано в моей последней статье. Для обеспечения равномерного утончения субстрата исследователи использовали VarioMill. Этот продукт использует лазерное химическое травление, пятиосную адаптивную микрообработку с ЧПУ и спектрометрию видимого/ИК-излучения для утончения задней стороны толщиной до 1 мкм. Цель здесь состоит в том, чтобы взять изображения SEM из IUA и сравнить их с золотым IC. Для SEM необходимо установить определенные параметры, чтобы получить эффективное изображение IUA, например, напряжение луча, поле зрения, время пребывания (скорость) и разрешение. С этими настройками микроскоп можно запрограммировать на отображение всей ИС.

Исследователи внесли изменения в уровень легирования, чтобы смоделировать активность троянца, который затем был получен с помощью РЭМ. В некоторых из этих примеров злоумышленник потенциально может заменить NAND на NOR, который, по сути, будет реализовывать собственную вредоносную логику с помощью таких методов, как модификация активной области, маскировка ячеек на 1-м металлическом слое или путем вставки/удаления логики на активной области (т.е. добавление инвертора).

Современные микроконтроллеры и ЦП имеют от 10 000 до миллиардов переходов, и для анализа потребуется множество изображений с микроскопа. Вот почему автоматизация играет ключевую роль, когда речь идет о сборе информации как о номинальных цепях, так и о цепях с троянами. Многообещающими оказались и другие проверенные методы, в частности тестирование задержки пути . В эксперименте Йеля исследователи вставили троянца на основе 2-битного компаратора рядом с входом ядра DES чипа. Задержки пути используются для создания отпечатков номинальных микросхем, поэтому каждый путь в списке соединений включается в состав трассы. Каждый отпечаток представляет собой один аспект общих характеристик подлинного дизайна. Затем чипы проверяются путем сравнения их параметров задержки пути с отпечатками пальцев, что довольно важно, когда речь идет о крошечных троянских схемах. В конечном итоге они смогли сделать вывод, что подлинными будут считаться только те чипы, чьи точки выборки находятся на пересечении всех заданных наборов во всем пространстве отпечатков пальцев или рядом с ним. Если одно или несколько мест выборки находились далеко от указанного пересечения, то считалось, что в чип вставлен троянец.

Теперь мы рассмотрим раздел, в котором аппаратный троян создается с помощью инструментов Electronic Design Automation (EDA) с открытым исходным кодом, чтобы показать, как он выглядит на уровне нестандартного дизайна.

ASIC Дизайн собственного HWT

Теперь, когда у нас была возможность узнать об аппаратных троянцах из множества разных источников, я подумал, что было бы интересно создать свой собственный от RTL до GDSII, где мы могли бы фактически просматривать наш чип с помощью программного обеспечения для 3D-рендеринга, такого как GDS3D. Прелесть разработки нашего собственного зараженного чипа заключается в том, что мы можем увидеть, как использовать инструменты с открытым исходным кодом для этого, а также иметь возможность смотреть на интегральную схему без микроскопа, поскольку мы можем увеличивать столько, сколько захотим, с помощью программного обеспечения. Давайте рассмотрим схему на уровне затвора обычной логической схемы И-ИЛИ с 4 входами рядом с той же схемой, но со вставленным трояном. Мы преобразуем это в код Verilog, а затем используем либо QFlow с OSU PDK, либо Openlane на Skywater130 PDK для создания файлов GDSII, чтобы мы могли просмотреть дизайн ASIC, как если бы мы смотрели на него через объектив с увеличением.

Дизайн внедренного троянца

По словам Димитриса Моуриса, Шарля Гуэрта и Нектариоса Георгиоса Цуцоса, ворота помечаются порядком оценки (первый G1, тогда G2, так далее.). Трассировка выполнения также показана в строках таблиц, которые будут отображать выходные данные четырех регистров конечного автомата (SM), которые определяются переменными r0 — r3. Выделенные и подчеркнутые значения в таблицах показывают, какая переменная моделирования была перезаписана после оценки логического элемента. На диаграмме (а) показана схема, которая выводит 1когда все четыре входа установлены на высокий уровень. На диаграмме (б) показана та же схема, что и (а), после внедрения примера троянца, который активируется только тогда, когда все входы установлены на 1.

У нас есть два способа преобразования логики уровня шлюза в Verilog: либо вручную, либо с помощью цифрового инструмента . Мы можем нарисовать схемы и преобразовать программное обеспечение в HDL по нашему выбору. Я выберу более ленивый вариант Б.

Код:

module active_hwt (

A,

B,

C,

D,

Y

); input A;

input B;

input C;

input D;

output Y; assign Y = ((((A & B) & (C & D)) ^ (((A & B) | (C & D)) | (C & D))) & D);endmoduleЭто довольно похоже на код без троянца, за исключением того, что этот код имеет операцию XOR вместе с дополнительным И с вводом C& D. Мы можем использовать EDA Playground для имитации волновых моделей, используя простой тестовый стенд для обоих. Если вы не знакомы с написанием тестовых стендов, вы можете посмотреть мой код , чтобы увидеть, как они написаны. По сути, мы проверяем входные данные A, B, C, & Dчтобы увидеть, как трудно было бы заметить разницу с точки зрения формы волны. Помните, что наша кривая должна показывать активацию трояна только тогда, когда у нас есть 4'b1111, все остальные входные и выходные сигналы должны отражать друг друга.

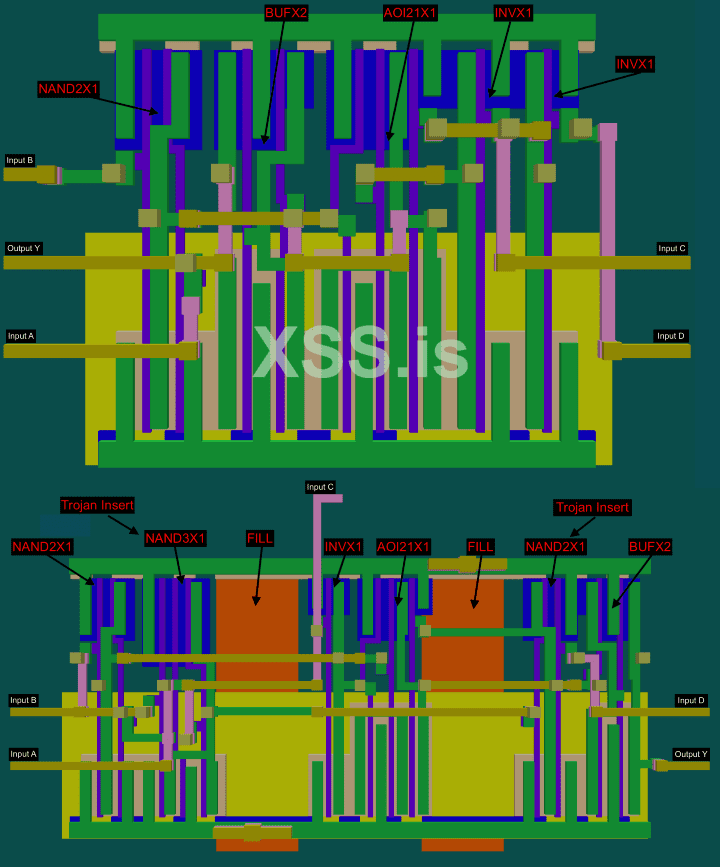

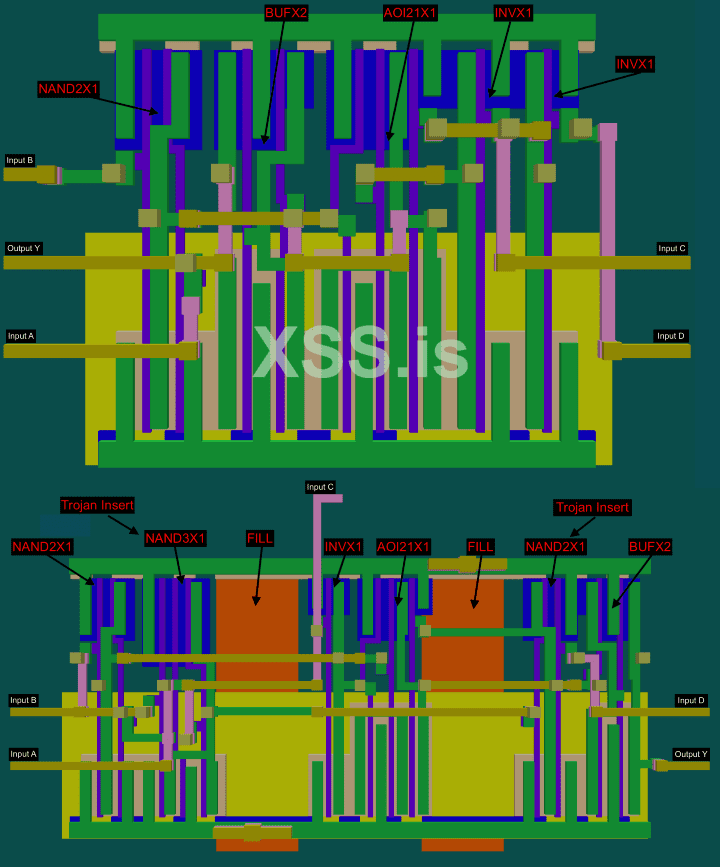

HWT не вставлен (сверху) HWT вставлен (снизу)

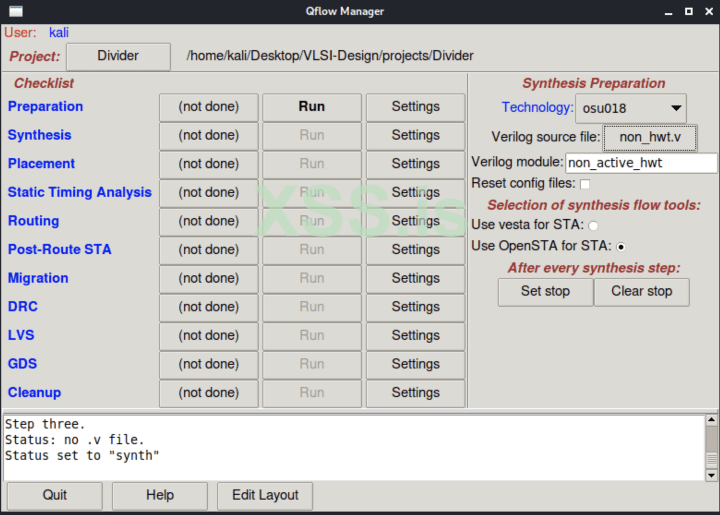

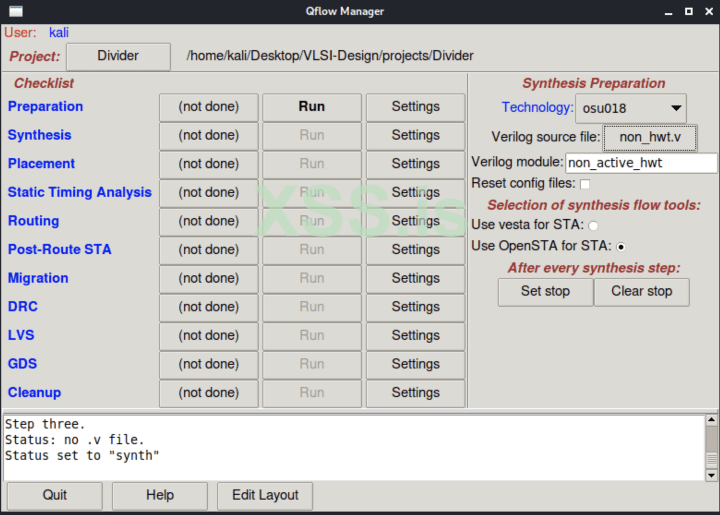

Оба они выглядят очень похожими с точки зрения того, как Yвключается и выключается, но если вы внимательно посмотрите на вывод сигнала без аппаратного трояна, вы увидите одно отличие. Когда Aчерез Dвсе переключились на 1, выход Yявляется 1как и ожидалось. Обратите внимание, когда мы проверяем те же входные данные со вставленным кодом HWT… вывод Yявляется 0когда все контакты активированы. Итак, мы нашли триггер троянца, а функционал обеих RTL-дизайнов практически идентичен. Вы можете видеть, что в строке 54 кода нашего тестового стенда, если бы мы забыли тест всех входов, установленных в активное состояние, сгенерированные формы сигналов обеих схем были бы идентичными. Давайте перейдем к предварительному изготовлению и посмотрим, как легко будет обнаружить различия между обеими конструкциями ASIC. Мы можем сделать это, пройдя процесс установки QFlow, где будут установлены все зависимости, такие как yosys , netgen , graywolf , qrouter и magic . Используя графический интерфейс QFlow, вы можете направить его к файлу Verilog, который вы хотите установить для подготовки к синтезу.

Графический интерфейс QFlow

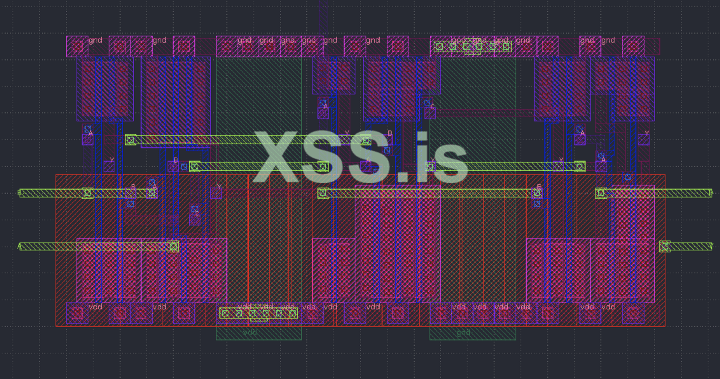

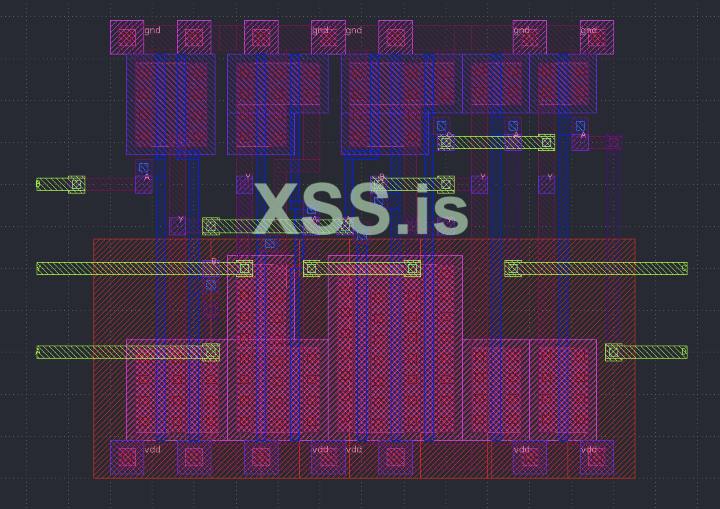

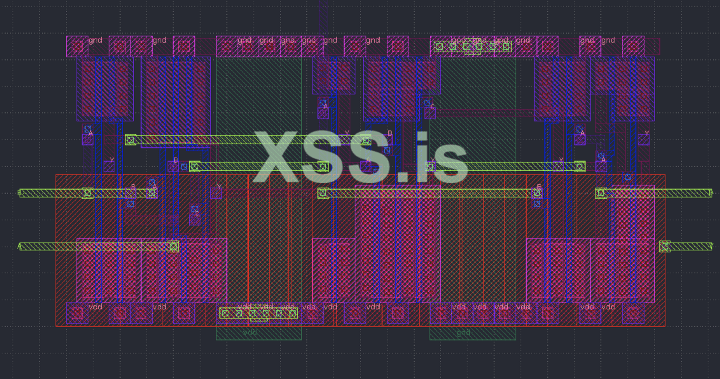

В выпадающем списке технологий у вас будет несколько вариантов, я решил выбрать последнюю версию PDK - OSU018. Это означает, что он будет спроектирован в масштабе 180 нм. После прохождения синтеза, размещения, STA, маршрутизации и т.д. В итоге вы получите файл .gds в каталоге /layout/. Используя Klayout, мы можем открыть файл GDSII в программе.

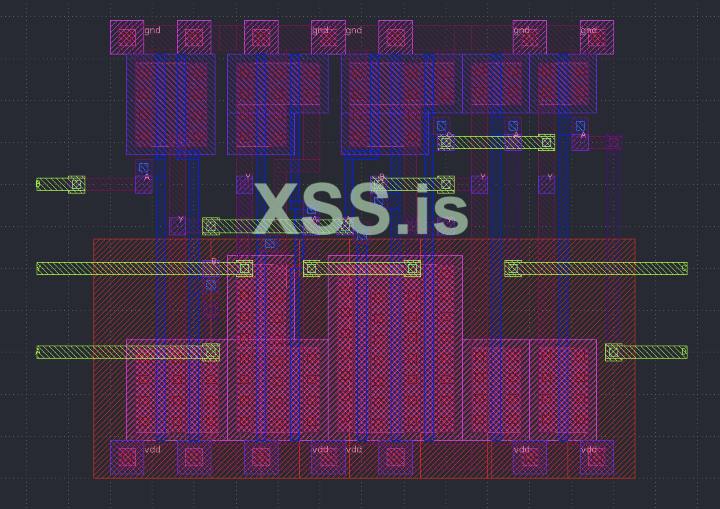

Если вы посмотрите на эту простую конструкцию ИС, она разбита на несколько простых логических вентилей. Первый из них - AOI21X1, это инверторный затвор AND-OR с 3 входами, который имеет функцию Y=!((A&B)|C).

При снятии слоев наша конструкция соответствует функции AOI и содержит 6 транзисторов PNP и NPN. Если сравнить эту конструкцию с конструкцией AOI21X1 во вставленном проекте HWT, то они выглядят совершенно одинаково. На самом деле обе конструкции содержат BUFX2 (неинвертирующий буфер [Y=A]), INVX1 (инвертор [Y=!A]) и NAND2X1 (двухвходовой NAND-затвор [Y=!(A&B)]). Давайте посмотрим, какие стандартные ячейки добавил наш зараженный дизайн.

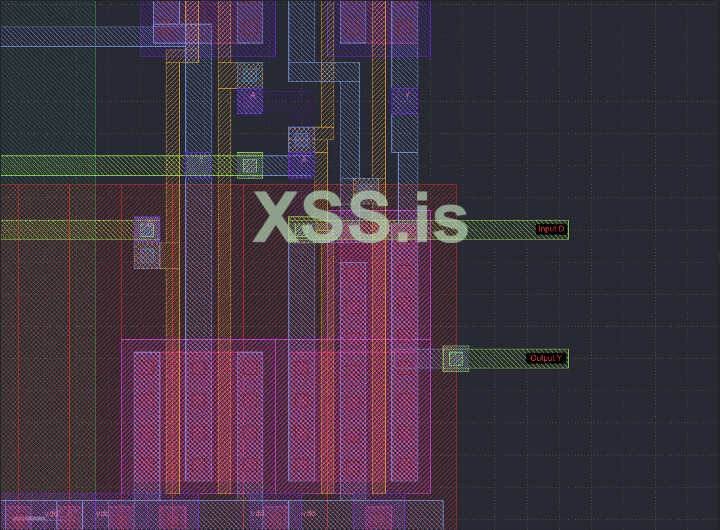

Как мы видим, это не так незаметно, как это было на уровне RTL-симуляции или даже вставки троянов на уровне легирования, потому что теперь кажется, что есть еще пара затворов. Наш дизайн показывает, что дополнительная ячейка, которая была добавлена, была NAND3X1 рядом с оригинальной NAND2X1. Кроме того, рядом с неинвертирующим буфером был добавлен дополнительный 2-входовой NAND-гейт.

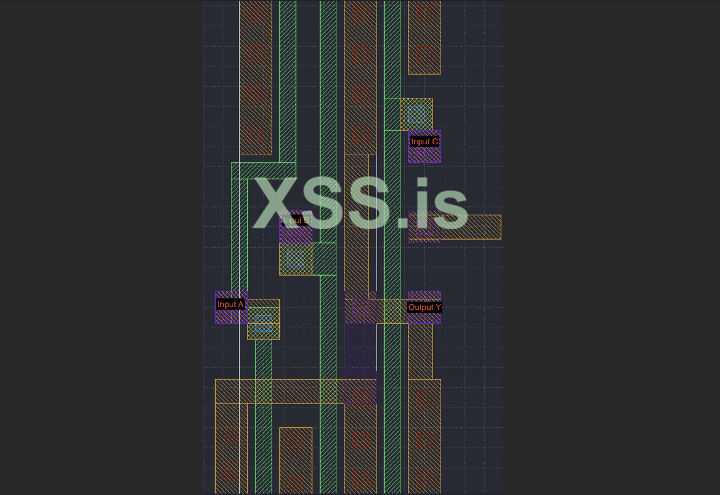

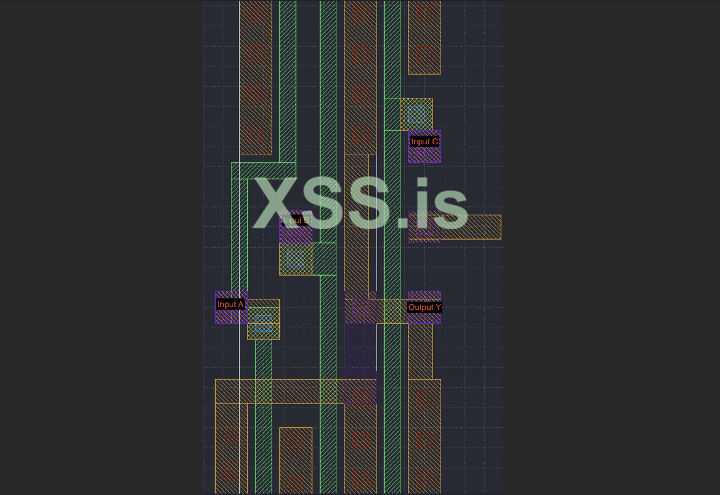

С левой стороны у нас есть 4 транзистора, составляющие наш 2-входовой NAND-затвор, а выход Y этого затвора подключен к входу A вставленного 3-входового NAND-затвора (с правой стороны), который влияет на выход этого затвора. Этот дополнительный затвор состоит из 6 транзисторов, что в общей сложности составляет дополнительные 10 транзисторов к зараженной конструкции ИС. Так где же все это соединяется, чтобы повлиять на фактический физический выходной вывод?

Добавляя слои обратно, мы видим, что верхний металлический (зеленый) слой показывает два физических вывода, вход D и выход Y. Дополнительные два NAND-затвора, вставленные в эту конструкцию, в конечном итоге изменят выход этого вывода, когда будет установлен определенный триггер, что в нашем случае означает, что все физические входные выводы установлены в 1. Сравнивая наш код Verilog с дизайном ИС, можно увидеть сходство между ними и то, почему было бы так трудно уловить их на некоторых этапах предварительной сборки. Мы можем взглянуть на 3D-модель, чтобы увидеть, как это будет выглядеть на пластине.

Если бы не дополнительные заполнители (две большие пустые оранжевые и желтые области), которые были автоматически размещены и маршрутизированы с помощью QFlow в нижней части конструкции HWT, они выглядели бы почти идентично, поскольку два дополнительных затвора, о которых говорилось ранее, не добавляют многого к конструкции.

Вам может быть интересно, в каком сценарии это будет вредоносно, отличный вопрос. Представьте, что эти четыре входных контакта, когда все они установлены в состояние HIGH, ожидают результата в виде выхода HIGH, который, по сути, позволяет микросхеме заблокировать процессор в состоянии без отладки. После того, как наша атака изменит конструкцию, она убедится, что когда все контакты установлены в положение HIGH, на выходе будет LOW. Это переведет процессор в состояние отладки, что позволит злоумышленникам или противникам узнать частную информацию и IP вашей SoC (System on Chip), которая не должна была стать общедоступной.

Заключение

В этой статье мы рассмотрели некоторые способы внедрения троянских программ, рассмотрели методы их обнаружения и разработали собственную программу с нуля, используя имеющиеся в моем распоряжении инструменты. Благодаря этому исследованию мы можем реально увидеть, как будет выглядеть зараженный чип со стороны цепочки поставок.

ВОТ репозиторий, содержащий все HDL и файлы проектирования, которые я создал на этапе исследования размещения и маршрутизации моей аппаратной троянской микросхемы.

Спасибо, что следили за мной! Надеюсь, вам понравилось так же, как и мне. Если у вас есть вопросы по этой статье, пожалуйста, напишите мне в Instagram: @hackersclub или Twitter: @ringoware

Счастливой охоты

использованная литература

- Форум технического руководства — Аппаратные трояны

- Трояны HW уровня Dopant

- Обнаружение аппаратных троянов, внедренных ненадежным Foundry, с помощью физического осмотра и расширенной обработки изображений

- Обнаружение аппаратных троянов с использованием порядка задержки пути

- Обнаружение аппаратного троянца с использованием отпечатка пальца задержки пути

- zk-Sherlock: разоблачение аппаратных троянов с нулевым разглашением

- Проникновение аппаратного троянца, запускаемого пороговым напряжением, в современную матрицу FPGA — методология обнаружения и смягчения последствий